INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:23.

- Laas verander 2025-01-23 12:53.

In hierdie handleiding gaan ons die FPGA gebruik om die eksterne LED -stroombaan te beheer. Ons gaan die volgende take uitvoer

(A) Gebruik die drukknoppies op FPGA Cyclone IV DuePrologic om LED te beheer.

(B) Flits -LED af en toe aan en uit

Video demo

Lab-spyskaart: https://roywchpi.blogspot.com 2020/06/10-fpga-dueprologic-push-button-led.html

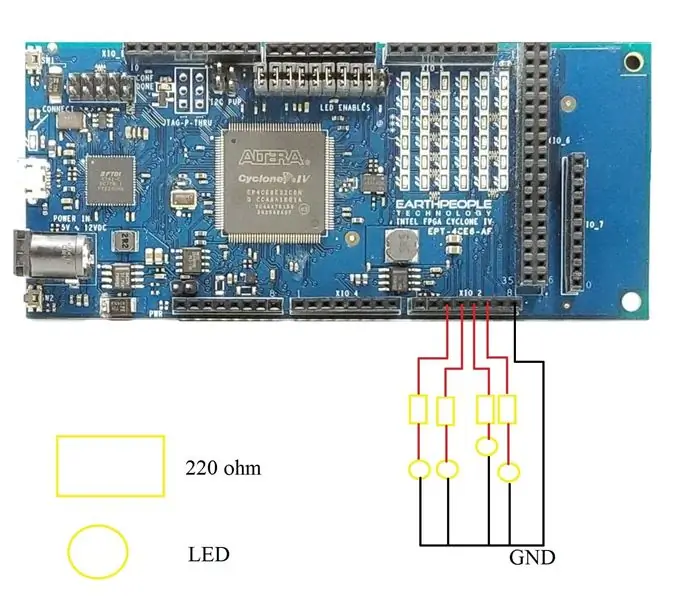

Stap 1: Bou 'n elektroniese stroombaan

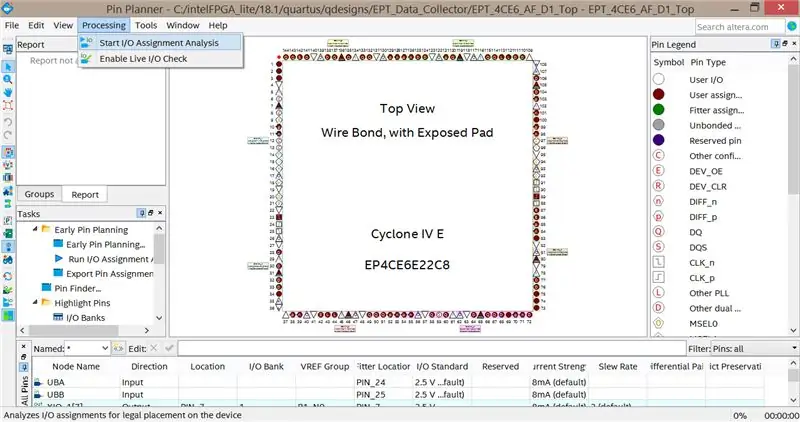

Stap 2: Gaan die penbeplanner na en wysig Verilog -kode

Stap 3: Wysig Verilog -kode

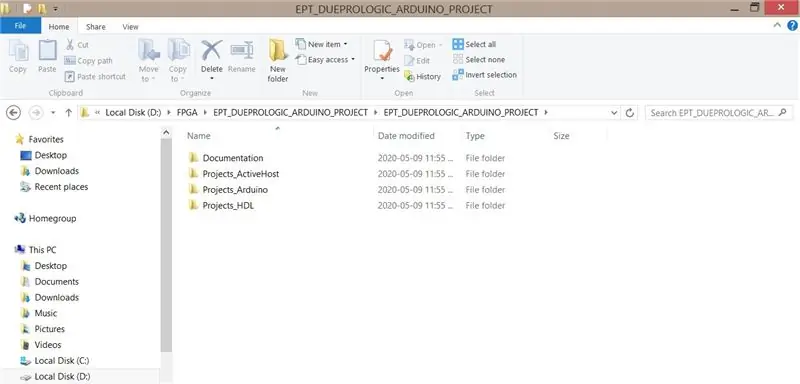

As u FPGA DueProLogic koop, moet u 'n DVD ontvang. Nadat u 'Projects_HDL' oopgemaak het, moet u die oorspronklike kode lêer sien

Voeg die gemerkte kode by. Dit registreer die I/O -poorte en ken nommers aan die poorte toe.

uitvoerdraad [7: 0] XIO_1, // XIO-D2-D9

uitvoerdraad [5: 0] XIO_2, // XIO-D10-D12

uitvoerdraad [5: 0] XIO_3, // XIO-D22-D29

invoerdraad [5: 0] XIO_4, // XIO-D30-D37

invoerdraad [5: 0] XIO_5, // XIO-D38-D45

uitvoerdraad [4: 0] XIO_6_OUT, // XIO-D46-D53

invoerdraad [31: 5] XIO_6, // XIO-D46-D53

uitvoerdraad [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

invoerdraad UBA, // drukknopskakelaars

invoerdraad UBB // drukknopskakelaars

ken XIO_1 [3] toe = start_stop_cntrl;

ken XIO_2 [1] toe = start_blinky; // LED flits LED aan en af

ken XIO_2 [2] = 1'b1 toe; // uitvoer HOOG

ken XIO_2 [3] = ~ UBA toe; // Druk knoppie A

ken XIO_2 [4] = UBB toe; // Druk knoppie B

ken c_enable = XIO_5 [2] toe;

ken LEDExt = XIO_5 [5] toe;

Dan moet ons 'n vertragingsteller instel. Lewer kommentaar op die oorspronklike timer -kode en skryf 'n nuwe timer -funksie

//-----------------------------------------------

// LED Knipperende begin

//-----------------------------------------------

/*

altyd @(stel CLK_66 of negeer RST)

begin

as (! RST)

begin_blinky <= 1'b0;

anders

begin

as (control_register [7: 4]> 0)

begin_blinky <= 1'b1;

anders

begin_blinky <= 1'b0;

einde

einde

*/

reg [31: 0] eks;

aanvanklike begin

eks <= 32'b0;

begin_blinky <= 1'b0;

einde

altyd @(posedge CLK_66)

begin

ex <= ex + 1'b1;

as (ex> 100000000) // flits aan/af ~ 1,6 sekondes, klok 66MHz

begin

start_blinky <=! start_blinky;

eks <= 32'b0;

einde

einde

//-----------------------------------------------

// LED -vertragingsteller

//-----------------------------------------------

/*

altyd @(posedge CLK_66 of negedge RST)

begin

as (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

anders

begin

as (meld [SELECT_MODE])

led_delay_counter <= timer_waarde;

anders as (meld [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

einde

einde*/

Stap 4: Stel Verilog -kode saam

Druk "Start Compilation" in Quartus, geen foutboodskap moet gegenereer word nie.

As u 'n foutboodskap oor verskeie penne ontvang. Gaan na Opdragte -> Toestel -> Toestel- en penopsies -> Penne vir twee doeleindes -> verander die waarde van die toepaslike pen in "Gebruik as gewone I/O".

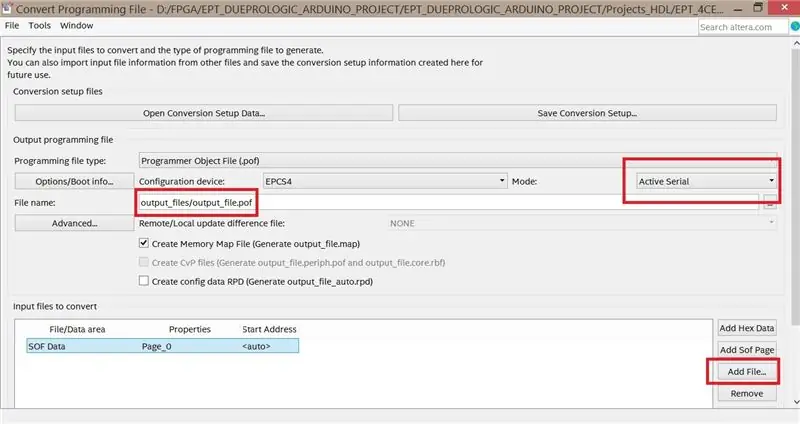

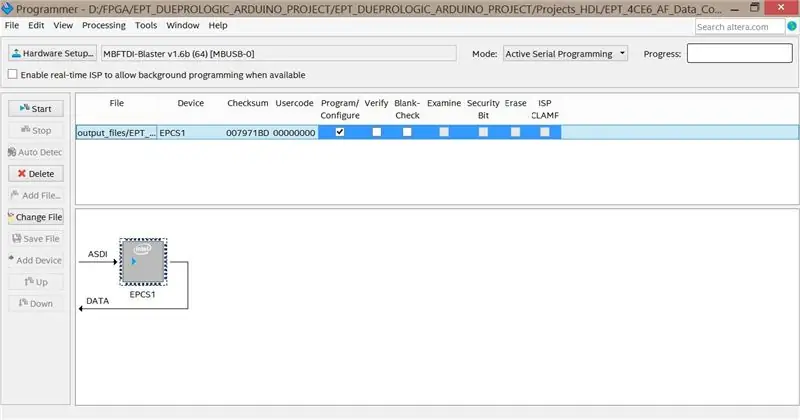

Na die samestelling moet u die pof -uitvoerlêer direk kry. As u sagteware nie op datum is nie, kan u slegs 'n sagte lêer kry. As dit gebeur, klik op "File" in Quartus -> "programmeer lêers omskakel". Verander die instellings wat met rooi blokkies gemerk is.

Stap 5: Kom ons probeer dit

Dit behoort immers te werk !!! Die geel LED is altyd aan. Die rooi LED flikker. Die blou LED is af as u op knoppie B. druk. Die groen LED is aan as u op knoppie A druk

Aanbeveel:

FPGA Cyclone IV DueProLogic Controls Raspberry Pi -kamera: 5 stappe

FPGA Cyclone IV DueProLogic Controls Raspberry Pi Camera: Ten spyte van die FPGA DueProLogic is amptelik ontwerp vir Arduino, gaan ons die FPGA en Raspberry Pi 4B oordraagbaar maak. FPGA om die hoek van

FPGA Cyclone IV DueProLogic Controls Servomotor: 4 stappe

FPGA Cyclone IV DueProLogic Controls Servomotor: In hierdie tutoriaal gaan ons Verilog -kode skryf om die servomotor te beheer. Die servo SG-90 word vervaardig deur Waveshare. As u die servomotor koop, ontvang u moontlik 'n datablad wat die werkspanning, maksimum wringkrag en die voorgestelde Pu

DIY VR-loopband- Basys3 FPGA-Digilent-wedstryd: 3 stappe

DIY VR-loopband- Basys3 FPGA-Digilent-wedstryd: wil u 'n VR-loopband bou waarop u u lessenaarprogramme en speletjies kan bestuur? Dan het u op die regte plek gekom! In konvensionele speletjies gebruik u die muis en die sleutelbord om met die omgewing te kommunikeer. Daarom moet ons die

Arduino Cyclone Game: 5 stappe (met foto's)

Arduino Cyclone Game: Ek het nog nooit die regte sikloon -arkadespel gespeel nie, maar ek hou van die idee om met ons reaksietyd te speel. Ek het 'n geminiaturiseerde spel ontwerp. Dit bestaan uit 32 LED's wat 'n sirkel vorm, die LED's brand een vir een as 'n geleide jaer. Die doel is om 'n knop te druk

Arduino Cyclone Arcade Game: 6 stappe

Arduino Cyclone Arcade Game: Knipperende flitsende ligte! Arduino! Spel! Wat meer moet gesê word? Hierdie speletjie is gebaseer op die Cyclone -arcade -speletjie, waar die speler probeer om 'n led te stop wat op 'n spesifieke plek om 'n sirkel draai