INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:24.

- Laas verander 2025-01-23 12:53.

Deur AmCoderhttps://www.linkedin.com/in/mituVolg meer deur die skrywer:

Oor: Mitu Raj - Net 'n stokperdjie en leerder - Chipontwerper - sagteware -ontwikkelaar - Fisika en wiskunde -entoesias Meer oor AmCoder »

## Dit is die gewildste skakel in Google vir VHDL -implementering van CORDIC ALGORITHM om sinus- en cosinusgolf te genereer ## Tans bestaan daar baie hardeware -doeltreffende algoritmes, maar dit is nie bekend nie as gevolg van die oorheersing van sagteware stelsels oor die baie jare. CORDIC is so 'n algoritme wat slegs 'n stel verskuiwing is en logika bygevoeg word wat gebruik word vir die berekening van 'n wye reeks funksies, insluitend sekere trigonometriese, hiperboliese, lineêre en logaritmiese funksies. Dit is die algoritme wat gebruik word in sakrekenaars, ens. Dus, deur eenvoudige shifters en adders te gebruik, kan ons 'n hardeware ontwerp met minder kompleksiteit, maar die krag van DSP met behulp van 'n koordalgoritme. Daarom kan dit as 'n kaal RTL -ontwerp in VHDL of Verilog ontwerp word sonder om 'n toegewyde dryfpunt -eenheid of komplekse wiskundige IP's te gebruik.

Stap 1: VHDL en Modelsim

Hier word die kordalgoritme geïmplementeer met behulp van VHDL om 'n sinus- en kose -golf te genereer. Dit kan sinus en cosinus van die invoerhoek met groot presisie uitvoer. Die kode is sintetiseerbaar op FPGA. Modelsim word gebruik om die ontwerp en die toetsbank te simuleer.

Stap 2: VHDL -kode vir die ontwerp en die toetsbank

Binêre skaaltegniek word gebruik om drywingsgetalle voor te stel.

Gaan deur die aangehegte dokumente voordat u kodeer.

Gaan deurSimulasie van cordic_v4.vhd - Die ontwerp - Die invoer is hoek in 32 bisse + tekenbit; dit kan enige hoek van 0 tot +/- 360 grade verwerk met 'n invoerpresisie van 0.000000000233 grade. By invoer -> MSB is die tekenbit en die res verteenwoordig 32 bisse. -Die uitset van die ontwerp is sy sinus en cos -waarde in 16 bisse + tekenbit.ie; met akkuraatheid 0.00001526. Let daarop dat die uitset in 2 se komplimentvorm vertoon word as die onderskeie sinus- of cos -waarde negatief is. Simulasie van testb.vhd - Toetsbank vir die ontwerp (1) Voer hoeke in en trek reset = '0'. Na twee stappe van simulasie, herstel na '1' en 'hardloop alles'. (2) Stel in die simulasievenster die radix van sin en cos seine as desimaal en formaat> Analoog (outomaties). (3) Zoom uit om die golfvorm te sien behoorlik.

Stap 3: lêers aangeheg

(1) cordic_v4.vhd - Ontwerp. (2) testb.vhd - toetsbank vir die ontwerp.

(3) Dokumenteer hoe om hoekinsette te dwing en die binêre resultate om te skakel.

Opdatering: HIERDIE LêERS WORD OBSELET EN WORD NIE MEER VERSKAF NIE. GEBRUIK ASB LêERS UIT VOLGENDE STAP

Stap 4: Mini -Cordic IP -kern - 16 bit

Beperking van die bogenoemde implementering is- stadige, laer klokfrekwensie as gevolg van berekeninge in 'n enkele kloksiklus. Mini-Cordic IP Core- 16 Bit

- Kritieke paaie versprei oor verskeie siklusse om prestasie te verbeter.- Vinniger- FPGA-beproefde ontwerp wat tot 100 Mhz-horlosie gesintetiseer word.- Meer gebied geoptimaliseer in HDL, minder hardeware.- Laai en klaar statusseine bygevoeg.- Die enigste nadeel is dat die resolusie minder is as die vorige. Toetsbank:

heeltemal outomaties van 0 tot 360 grade hoekinsette

Aangeheg lêers: 1) mini cordic main vhdl file2) mini cordic toetsbank3) Mini Cordic IP Core handleiding 4) Doc oor hoe om hoeke te dwing en resultate om te skakel

Vir enige navrae, kontak my gerus:

Mitu Raj

volg my:

pos: iammituraj@gmail.com

### Totale aflaaie: 325 tot 01-05-2021 ###

### Kode laas gewysig: 07-07-2020 ###

Aanbeveel:

Beheer oor die hele wêreld met behulp van internet met behulp van Arduino: 4 stappe

Beheer oor die hele wêreld met behulp van internet met behulp van Arduino: Hallo, ek is Rithik. Ons gaan 'n internetbeheerde LED maak met u telefoon. Ons gaan sagteware soos Arduino IDE en Blynk gebruik. Dit is eenvoudig, en as u daarin geslaag het, kan u soveel elektroniese komponente beheer as wat u wil

Monitor versnelling met behulp van Raspberry Pi en AIS328DQTR met behulp van Python: 6 stappe

Monitering van versnelling met behulp van Raspberry Pi en AIS328DQTR Gebruik van Python: Versnelling is eindig, volgens ek volgens sommige wette van die fisika.- Terry Riley 'n Jagluiperd gebruik ongelooflike versnelling en vinnige spoedveranderinge wanneer hy jaag. Die vinnigste wesens aan wal gebruik af en toe sy hoogste tempo om prooi te vang. Die

Selfbalanserende robot met behulp van PID -algoritme (STM MC): 9 stappe

Selfbalanserende robot met behulp van PID -algoritme (STM MC): Onlangs is baie werk gedoen aan die selfbalansering van voorwerpe. Die konsep van selfbalansering het begin met die balansering van die omgekeerde slinger. Hierdie konsep het ook uitgebrei tot die ontwerp van vliegtuie. In hierdie projek het ons 'n klein mod

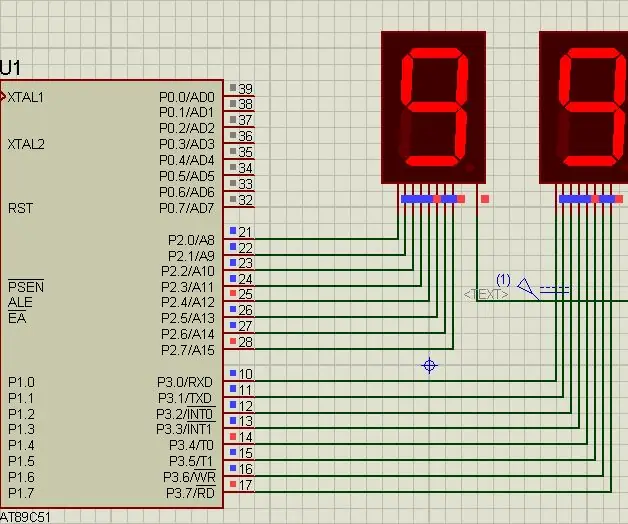

Hoe om van 0 tot 99 te tel met behulp van 8051 mikrobeheerder met 7 segmentweergawe: 5 stappe (met foto's)

Hoe om van 0 tot 99 te tel Met behulp van 8051 mikrobeheerder met 7 -segmentweergawe: Hallo almal, in hierdie tutoriaal gaan ons u vertel hoe om van 0 tot 99 te tel met twee 7 -segment -skerms

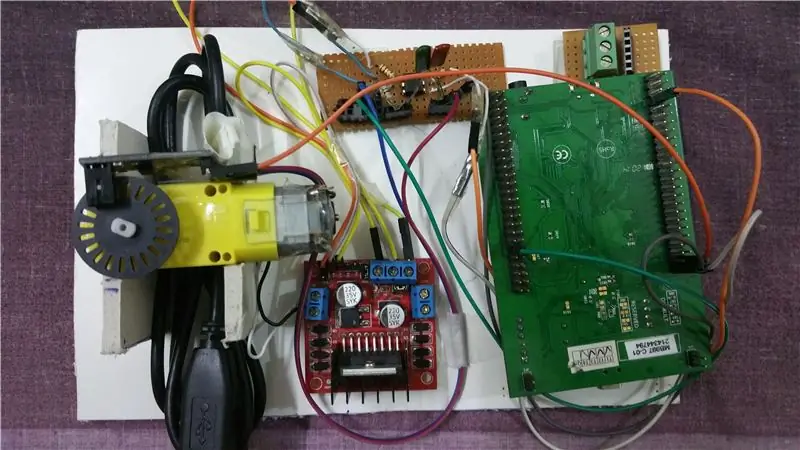

Snelheidsbeheer van DC -motor met behulp van PID -algoritme (STM32F4): 8 stappe (met foto's)

Snelheidsbeheer van DC -motor met behulp van PID -algoritme (STM32F4): hallo almal, dit is 'n ander projek. Hierdie keer is dit STM32F407 as MC. Dit is 'n einde van die middel semester projek. Hoop jy hou daarvan. Dit verg baie konsepte en teorie, daarom gaan ons eers daarop in. Met die koms van rekenaars en die