INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:23.

- Laas verander 2025-01-23 12:53.

JDM is 'n gewilde PIC -programmeerder omdat dit 'n seriële poort, 'n minimum van komponente gebruik en geen kragtoevoer benodig nie. Maar daar is verwarring, met baie programmeerdervariasies op die internet, watter werk met watter PIC's? In hierdie 'instruerbare' toets ons JDM en ek demonstreer hoe u die kring kan simuleer met Spice, wat al u vrae sal beantwoord!

Voorrade

LTspice wat hier van Analog Devices afgelaai kan word.

U benodig ook die JDM -kringlêers hier.

Stap 1: Vereistes vir reekspoort

JDM benodig 'n seriële poort wat aan die EIA232-spesifikasie voldoen, ideaal met +12/-12 spanningsvlakke.

Volgens die Texas Instruments Line Driver MC1488 -datablad (Figuur 3)

Uitgangsimpedansie = 4V/8mA = 500 ohm.

Kortsluitstroomlimiet = 12mV, sonder tydsbeperking - geen skade aan chip nie.

Invoerimpedansie van lynontvanger = 3k tot 7k ohm aanbeveel.

Seriële poorte op ouer tafelrekenaars gebruik +12v/-12V wat aan hierdie vereiste voldoen.

Seriële poorte op nuwer skootrekenaars gebruik laer spanning. JDM werk al dan nie - die antwoord is meer kompleks.

Stap 2: Vereistes vir PIC -programmering

Inligting oor PIC -programmeringsvereistes word verkry van Microchip. Bogenoemde is vir 'n tipiese toestel.

Stap 3: JDM -spesifikasie

Het die oorspronklike JDM -webwerf in die newel van tyd verlore geraak? Dit laat ons raai wat die ontwerper oorspronklik vir die spesifikasie bedoel het.

- Verskaf VDD = 5V, en tot IDD = maksimum 2mA (vir 'in socket' weergawe)

- Verskaf VHH = 13V, en tot IHH = 0.2mA maksimum.

- MCLR Stygtyd tVHHR = 1uS maks.

- ICSP-weergawe moet MCLR laag kan trek teen 22k-optrek op die teiken.

Stap 4: Kringbeskrywing

Figuur JDM1 is gebaseer op die 'standaard' JDM -stroombaan wat van die PICPgm -webwerf geneem is. Dit is die 'PIC in Socket' programmeerder waar PIC krag kry van TX- en RTS -penne. Die oorspronklike diagram was moeilik om te verstaan, so ek het dit oorgeteken met behulp van die normale gang van stroom na bo. En ek het LED -aanwysers "RESET", "PROG" en "RTS" bygevoeg wat nodig is tydens konstruksie en toetsing. Hopelik het dit geen nadelige uitwerking op gedrag nie.

Die normale konvensie van stroombaanontwerp is algemeen, maar die belangrikste kenmerk van JDM is dat die seriële poortgrond (GND) aan VDD gekoppel is. Dit skep verwarring omdat seriële poortseine gemeet word met betrekking tot GND, PIC -seine met betrekking tot logiese grond (VSS).

As TX hoog word, tree Q1 op as twee voorwaartse voorspelde diodes. (Q1 -versamelaar is nie omgekeerd bevooroordeeld soos met normale transistorbedryf nie). Q1 -kollektor laai C2, wat by VDD+8V deur Zener (D3) vasgeklem word. Q1 -emitter lewer 13V aan MCLR vir die program-/verifikasiemodus.

As TX laag word, word kapasitor C3 deur D1 gelaai en VSS word vasgemaak by VDD-5V deur zener (D5). TX word ook vasgeklem (VSS-0.6) met D1. Q1 is af, C1 hou sy lading vir die volgende programmeringspuls. MCLR word by 0V vasgemaak deur D2, sodat die PIC nou herstel is.

As die RTS hoog is, word die klok na PGC gestuur. D4 klem PGC by VDD logika hoog. As RTS laag is, word kapasitor C3 deur D6 gelaai en VSS word vasgemaak by VDD-5V deur zener (D5). D6 klem PGC by VSS of logika 0 vas.

Tydens die programmering word data wat op DTR gestuur word, gelees op PGD, wat die PIC as invoer opstel. As DTR hoog is, tree Q2 op as 'emittervolger' en PGD-spanning is ongeveer (VDD-0.6) of logies 1. As DTR laag is, tree Q2 op as 'n slegte transistor (emitter- en kollektorpennetjies omgekeer). Q2 trek PGD laag, wat deur D7 vasgeklem word by VSS of logika 0.

Tydens die verifikasie stel die PIC PGD as 'n uitset in om data na die seriële poort te stuur. DTR moet hoog gestel word en data word gelees op CTS. As die PGD -uitset hoog is, is Q2 af, CTS = DTR = +12V. As PGD -uitset laag is, is Q2 aan. Q2 -versamelaar trek stroom (12V+5V)/(1k+1k5) = 7mA van DTR af, en trek CTS laag na VSS.

Stap 5: Berei voor vir simulasie

Laai LT -speserye af, stoor en maak die kringlêers (*.asc) hier oop. Om die stroombaan te simuleer, moet ons 'n paar insette gee en dan die uitsette "naspeur". V1, V2 V3 simuleer die 12V -seriële poort met uitgangsimpedansie R11, R12, R13.

- V1 genereer 2 programpulse op TX van 0.5ms tot 4.5ms

- V2 genereer burst van datapulse op DTR van 1,5 tot 4,5 ms

- V3 genereer burst van klokpulse op RTS van 0,5 tot 3,5 ms

Die komponente V4, X1, R15 en R16 is almal deel van die simulasie.

- V4 genereer 2 pulse van 2,5 tot 4,5 ms vir die verifiëring van data.

- Trui X1 simuleer OUTPUT op PGD.

- R15, R16 simuleer die "laai" van PIC op VDD en MCLR.

Stap 6: Wysigings vir ICSP

Figuur JDM3 toon die weergawe vir "in kring" -programmering. Wysigings van die oorspronklike is

- Vervang die ZIF -aansluiting met die ICSP -aansluiting.

- Die PIC word nou aangedryf deur 'n toevoer na die doelkring (V5).

- Verwyder 5V zener (D5).

- Die klein 100pF -kondensator (C4) word langs die PIC op die teikenbaan geskuif.

- LED's neem waar moontlik krag uit die printplaat.

- Die MCLR-optrekweerstand (R10) en diode (D10) word benodig op die teikenskring.

- WAARSKUWING. Die teikenbord moet 'n "drywende" toevoer hê, verkieslik 'n battery.

- Moenie die doelgrond (VSS) aan die rekenaar-/rekenaargrond koppel nie deur enige ander rekenaarpoort op dieselfde tyd as JDM aan te sluit.

Na die simulasie van JDM1, het die probleem van lang laaityd op C2 duidelik geword. Na die lees van Fruttenboel blyk dit dat C2 en Q1 bygevoeg is as 'n wysiging van die oorspronklike. Ek kan nie dink wat C2 en Q1 bedoel is om te doen nie, behalwe om probleme te veroorsaak. So vir JDM4 keer ons terug na die ouer ontwerp op Fruttenboel, wat eenvoudig en eenvoudig is om te verstaan. D1 en D3/LED2 klem MCLR tussen VSS en VDD+8V. Die waarde van R1 word verminder tot 3k3, net genoeg om LED2 by 12V te verlig.

JDM4 is ook ontwerp om te werk met swakker seriële poorte. As TX hoog word (+9V), is TX-stroombron = (9-8)/(1k +3k3) = 0,2ma, net genoeg om MCLR hoog te trek, hoewel dit onvoldoende is om LED2 te verlig. As TX laag word (ongeveer -7V), sink die stroom van TX = (9-7)/1k = 2mA. LED1 stroom = (7-2 vir led)/(2k7) = 1.8mA. MCLR aftrekstroom = 7-5,5/3k3 = 0,5mA.

Hierdie stroombaan is ook getoets (JDM5-simulasie) om te sien wat met die seriële poorte +/- 7V minimum gebeur, waar daar onvoldoende spanning is om VHH = 13V te onderhou. Die doel van C1 word nou duidelik, C1 skep 'n kort +ve hupstoot vir MCLR, 'n styging van 33us aan die stygende rand van TX, moontlik lank genoeg om die PIC in die programmeermodus te kan kry, miskien? Maar verwyder jumper X2 (skakel LED1 uit) aangesien daar nie genoeg stroom is om MCLR laag te trek en LED1 saam te verlig nie. As TX laag word, sink die TX-stroom = (7V-5.5V)/(1k+3k3) = 0.3mA, net genoeg om MCLR laag teen die optel-R10 te trek.

Stap 7: Simulasie -resultate

Om die grafiese lêers te sien, is dit beter om met die rechtermuisknop op die onderstaande skakels te klik en dan 'Open skakel in nuwe oortjie' te kies

Simulasie 1: spoor van MCLR, VSS en RTS vir oorspronklike JDM1. Onmiddellik is waarneming 1, 2 en 3 duidelik.

Simulasie 2: spoor van MCLR en VSS, en RTS vir gemodifiseerde JDM2, wat vorige probleme oplos.

Simulasie 3: spoor van PGD, VSS en PGC vir JDM2 wat data in programmodus stuur. Waarneming 4 by 3.5mS.

Simulasie 4: spoor van PGD, VSS en CTS vir JDM2 in die verifikasiemodus (jumper X1 ingevoeg). OK

Simulasie 5: spoor van MCLR, VSS, PGD en PGC vir JDM3. ICSP met krag uit stroombaan los baie probleme op.

Simulasie 6: spoor van MCLR, VSS, PGD en PGC vir JDM4 met +/- 9V seriële poort. MCLR styg onmiddellik en werk ten volle.

Simulasie 7: spoor van MCLR, VSS en TX vir JDM5 met +/- 7V seriële poort en jumper X2 verwyder. C1 skep 'n +ve hupstoot (piek) op die stygende rand van MCLR, amper voldoende om MCLR bo TX na 13V te stoot.

Stap 8: Gevolgtrekkings

Spice is baie goed in die onthulling van 'verborge geheime' van die werking van die kring. Die JDM -kring werk klaarblyklik en is verenigbaar met baie PIC -skyfies, maar die volgende waarnemings toon moontlike beperkings/verenigbaarheidsprobleme/foute aan?

- Lang stygtyd van MCLR terwyl C2 op die eerste pols van TX na VPP laai. Misluk spesifikasie 3.

- Die reekspoort laai C2 wanneer TX hoog word en RTS laag. Maar RTS het ook die taak om C3 te laai. As beide gelyktydig plaasvind, veroorsaak dit meer las op RTS, gevolglik verloor C3 lading (VSS styg) teen 2 ms by simulasie. Misluk spesifikasie 1.

- C3 verloor lading (VSS begin styg) nadat klokpulse op 3,5 ms stop.

- Wat is die doel van C2, is dit enigsins nodig?

Oplossings

- Vermoedelik gebruik PICPgm 'n 'werk-om' -programmatuur. Dit moet 'n lang TX -pols toepas om voor te laai na C2, en dan eers na die tweede TX -puls die programmeermodus binnegaan? Vir simulasie het ek die waarde van C2 tot 1uF verminder om 'n stygingstyd van 1 ms te gee. Nie 'n ideale oplossing nie.

- Verdeel C2 en C3 sodat hulle onafhanklik laai. Een klein aanpassing aan JDM2, C2 word verwys na GND in plaas van VSS.

- Opgelos deur JDM3. ICSP is baie meer betroubaar, aangesien PIC aangedryf word deur 'n teikenbaan.

- JDM4 los probleem 1. Dit is 'n eenvoudige ontwerp wat C2 heeltemal uitskakel.

Stap 9: En laastens

Die bewys van die poeding is in die eet. Hierdie JDM werk, so hou aan om dit te gebruik.

En my aanbevelings is:

- gebruik JDM2 vir in -socket programmering en 12V seriële poorte,

- gebruik JDM4 vir ICSP-programmeerder en seriële poorte bo +/- 9V,

- gebruik JDM4 met trui X2 verwyder vir seriële poorte bo +/- 7V.

Verwysings:

Analog Devices LT -speserye

picpgm

Fruttenboel

Volg meer PIC-projekte op 'n sluwe hoek

Aanbeveel:

Spelontwerp in vyf stappe: 5 stappe

Spelontwerp in fliek in 5 stappe: Flick is 'n baie eenvoudige manier om 'n speletjie te maak, veral iets soos 'n legkaart, visuele roman of avontuurlike spel

Elegoo Super Started Kit Uno R3 Review: 4 stappe

Elegoo Super Started Kit Uno R3 Review: 'n Paar dae gelede het Elegoo vir my hierdie Super Starter Kit gestuur om te toets. Dus, laat ons kyk wat daarbinne is. By die opening van hierdie kompakte behuizing kan ons baie dinge sien. Op die omslag is 'n indeks met al die komponente. Binne het ons 'n dankkaart met al die

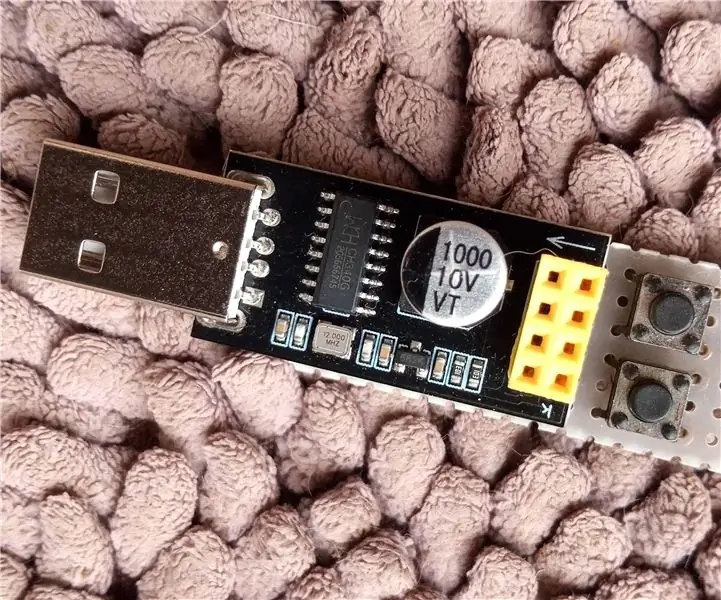

ESP -01 Programmer Hack - the Easy One :): 6 stappe

ESP-01 Programmer Hack-the Easy One :): Hallo ESPers, in hierdie instruksies sal ek u 'n eenvoudige hack wys om 'n programmeerder vir die ESP-01 / ESP8266-01 / ES-01-module te maak. Die meeste van ons het 'n Arduino-bord of FTDI USB-TTL-toestelle as programmeerders vir hierdie module gebruik. Beide metodes werk goed. Maar t

(byna) Universal MIDI SysEx CC Programmer (en Sequencer ): 7 stappe (met foto's)

(byna) Universal MIDI SysEx CC Programmer (en Sequencer …): In die middel tagtigerjare het synth -vervaardigers 'n " less is better " proses wat gelei het tot kaalbene -sintese. Dit het die verlaging van die koste aan die vervaardiger se kant moontlik gemaak, maar het die lapproses tediuos gemaak, indien nie onmoontlik vir die finale gebruik nie

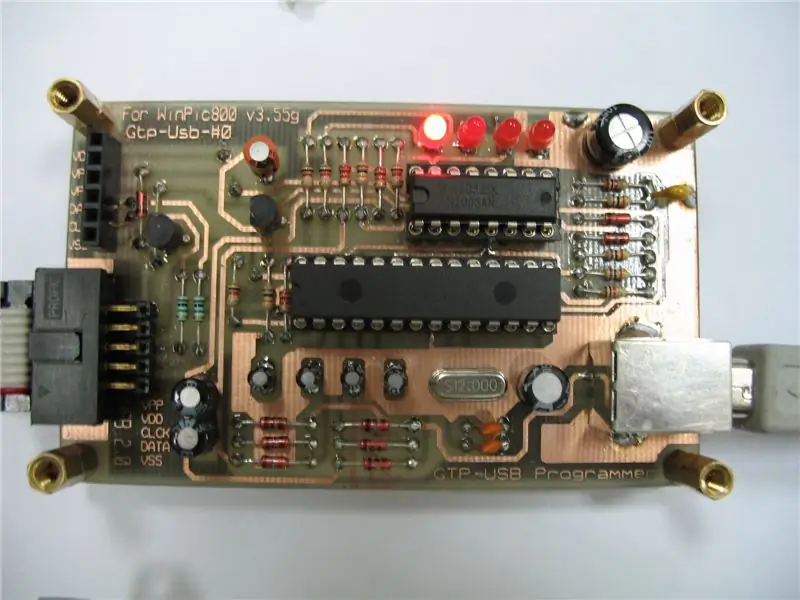

GTP USB PIC PROGRAMMER (Open Source): 5 stappe (met foto's)

GTP USB PIC PROGRAMMER (Open Source): Hierdie werk bevat GTP USB (nie plus of lite nie). Die skematiese, foto's en PCB is ontwikkel deur PICMASTERS op grond van 'n paar waardevolle werke wat voorheen gedoen is. Hierdie programmeerder ondersteun pic10F, 12F, 16C, 16F, 18F, 24Cxx Eeprom. Ongelukkig wou dit