INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:24.

- Laas verander 2025-01-23 12:53.

Koppel u Mojo -ontwikkelingsbord aan eksterne insette met hierdie skild.

Wat is die Mojo -ontwikkelingsraad?

Die Mojo -ontwikkelingsraad is 'n ontwikkelingsraad wat gebaseer is op die Xilinx spartan 3 FPGA. Die bord is gemaak deur Alchitry. FPGA's is baie handig waar verskeie prosesse gelyktydig uitgevoer moet word.

Wat sal jy nodig hê?

Voorrade

Mojo -ontwikkelingsraad

Gerber lêer

8 x 15k ohm weerstande (opsioneel*)

4 x 470 ohm weerstande

4 x 560 ohm weerstande

4 x CC sewe segment vertoon

4 x 3 mm LED's

4 x SPDT tasbare skakelaars

1 x 4 posisie DIP -skakelaar op die oppervlak

2 x 25 by 2 of 4 x 25 opskrifte

1x 2 by 5 pen bokskop

Soldeerbout

Soldeer

Fluks

*(as hierdie weerstande weggelaat word, moet interne pullup/down -down vir relevante penne geaktiveer word)

Stap 1: Laai Gerber op na die vervaardiger van u keuse

Vir my borde het ek by JLC PCB bestel.

Die enigste verandering wat ek aangebring het, was die kleur wat ek wou pas by die swart van die Mojo.

Stap 2: Raadsvergadering

By soldeer vind ek dit altyd nuttig om eers die laagste dele te soldeer, dus dit is 'n goeie idee om met die weerstande te begin.

R5, R6, R7, R8, R9, R10, R11 en R12 is 15k ohm weerstande wat gebruik word om die skakelaars af te trek (ignoreer dit as u interne pullup/pull down gebruik).

R1, R2, R3, R4 is 560 ohm weerstande wat verantwoordelik is vir die beperking van die stroom deur die 7 segment vertoning.

R13, R14, R15, R16 is 470 ohm weerstande wat verantwoordelik is vir die beperking van die stroom deur die 4 LED's.

Soldeer dan die dipskakelaar, tasbare skakelaars, LED's, sewe segmentskerms en boksopeningskoppelstuk in die volgorde.

Plaas nou die 25 by 2 (of 2 25 by 1) in die mojo om die penne in lyn te bring. Rig die skild met die penne in en soldeer dit op hul plek.

Stap 3: sagteware -opstelling

Vir sagteware wat na die Alchitry -webwerf verwys, sal u weet wat u nodig het om die Xilinx ISE te begin en te installeer. Maar verander die.ucf -lêer sodat dit weet watter penne gekoppel is aan wat belangrik is om u program aan die gang te kry.

Hier is die.ucf -lêer wat ek saam met die skild gebruik:

KONFIGEER VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODE "clk" 50 MHz HOOG 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sewe [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sewe [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sewe [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sewe [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Onthou as u nie die aftrekweerstands geïnstalleer het om die penne in die.ucf mee te wysig nie

| AFTREK; o

| OPTREK;

As u die blok vir enigiets wil gebruik, is die verbindings soos volg. Links is die blokspeldnommer en regs die mojo -speldnommer wat u in u.ucf moet toewys:

pen 1 = 29

pen 2 = 51

pen 3 = 32

pen 4 = 41

pen 5 = 34

pen 6 = 35

pen 7 = 40

pen 8 = 33

pen 9 = GND

pen 10 = +V

Aanbeveel:

DIY ESP32 Development Board - ESPer: 5 stappe (met foto's)

DIY ESP32 Development Board - ESPer: Ek het onlangs gelees oor baie IoT's (Internet of Things) en vertrou my, ek kon net nie wag om een van hierdie wonderlike toestelle te toets nie, met die vermoë om aan te sluit op die internet, myself en kry my hande op die werk. Gelukkig is die geleentheid

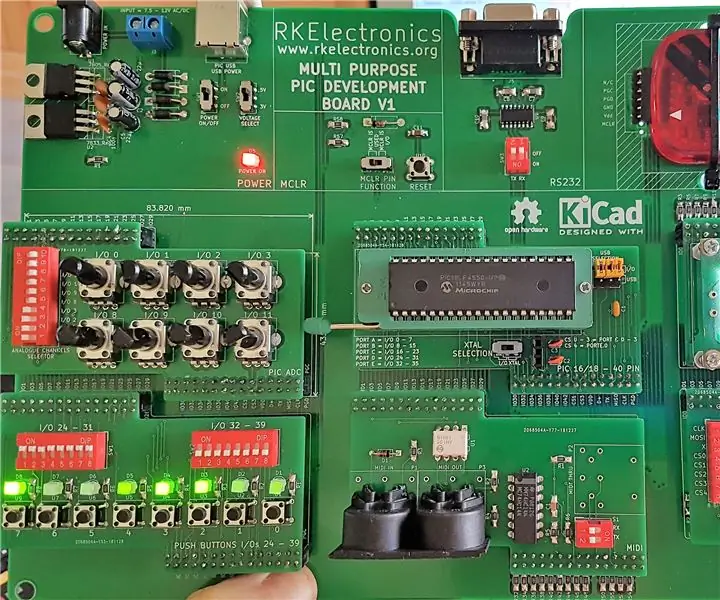

JALPIC One Development Board: 5 stappe (met foto's)

JALPIC One Development Board: As u my Instructables -projekte volg, weet u dat ek 'n groot fan is van die JAL -programmeertaal in kombinasie met die PIC Microcontroller. JAL is 'n programmeertaal wat soos Pascal ontwikkel is vir die 8-bis PIC-mikrobeheerders van Microchip. Ma

PIC Microcontroller Development Board System: 3 stappe

PIC Microcontroller Development Board System: Hierdie projek is vir die ontwerp en gebruik van 'n PIC -ontwikkelingshulpmiddel wat buigsaam is vir 'n wye verskeidenheid PIC -gebaseerde elektroniese projekte. Dit is dikwels makliker om mikrokontroller -projekte te ontwikkel met behulp van ontwikkelingshulpmiddels; wat gebruikersgebaseerd toelaat

WIDI - Draadloos HDMI met behulp van Zybo (Zynq Development Board): 9 stappe (met foto's)

WIDI - Draadlose HDMI met behulp van Zybo (Zynq Development Board): het u al ooit gewens dat u u TV as 'n eksterne monitor aan 'n rekenaar of skootrekenaar kon koppel, maar wou u nie al die lastige toue in die pad hê nie? As dit die geval is, is hierdie tutoriaal net vir u! Alhoewel daar 'n paar produkte is wat hierdie doel bereik, is 'n

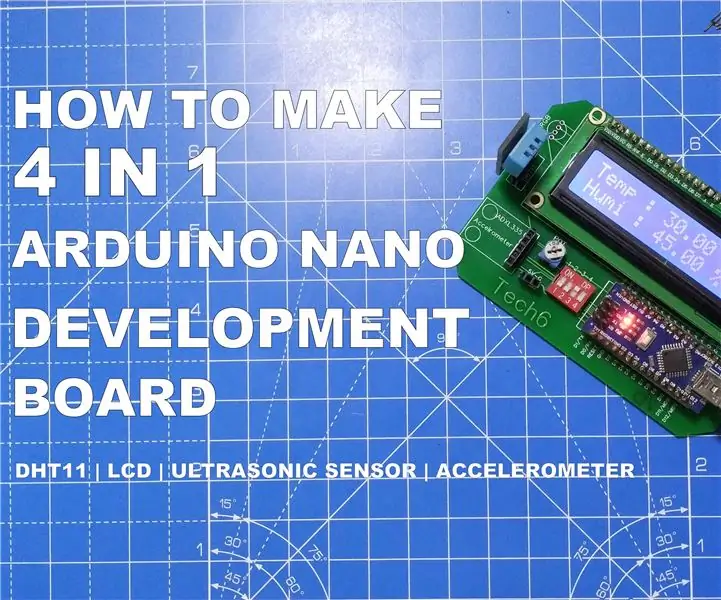

Hoe om 'n 4-in-1 Arduino Nano Development Board te maak: 4 stappe

Hoe om 4-in-1 Arduino Nano Development Board te maak: In hierdie instruksies leer u hoe u 'n Arduino Nano-ontwikkelingsbord kan maak. Die Arduino nano-ontwikkelingsbord het ingeboude gleuwe vir ultrasoniese sensor (HCSR-04), versnellingsmeter, DHT11-sensor en Liquid Crystal Display (LCD). Hierdie bo