INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:25.

- Laas verander 2025-01-23 12:53.

Ons doel met hierdie projek was om iets te skep wat gemeenskappe energie en finansiële hulpbronne kan bespaar. Bewegings geaktiveerde straatligte sou albei hierdie dinge doen. Regoor die land word energie gemors op straatligte wat strate wat leeg is, aansteek. Ons straatligstelsel verseker dat die ligte net brand wanneer dit nodig is, en dit bespaar gemeenskappe talle dollars. Deur bewegingsensors te gebruik, skakel die stelsel slegs ligte aan as motors teenwoordig is. Ook vir die veiligheid van voetgangers het ons 'n oorheersingsknoppie geïmplementeer wat alle ligte op straat aanskakel. Die volgende stappe lei u deur hoe ons ons afgeskaalde model van die projek ontwerp en gebou het met behulp van Vivado en 'n Basys 3 -bord.

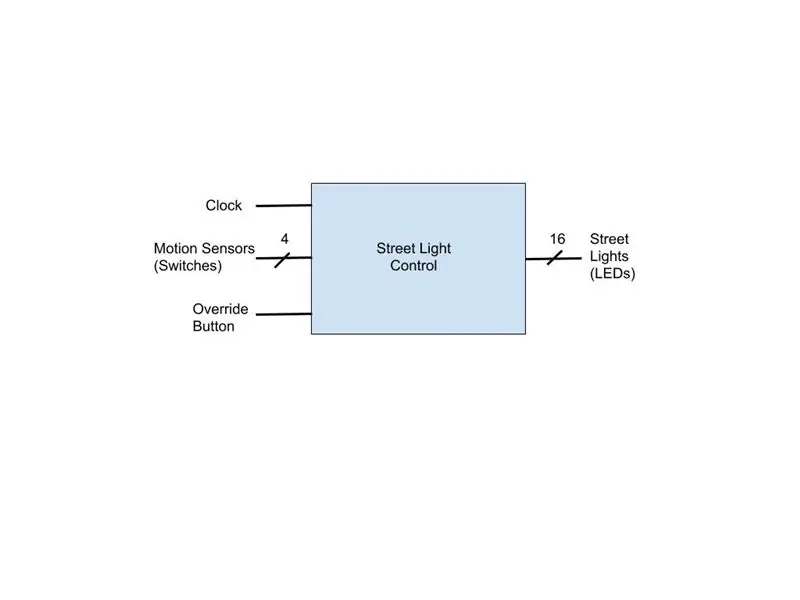

Stap 1: System Black Box

Ons het hierdie projek begin deur 'n eenvoudige swart boksdiagram te teken. 'N Black box -diagram toon eenvoudig die insette en uitsette wat ons stelsel benodig om alle nodige prosesse te voltooi. Ons het probeer om ons ontwerp so eenvoudig en basies moontlik te hou. Ons drie stelsel -insette het 'n bus bewegingsensors ingesluit (4 vir ons afgeskaalde model), 'n voetgangersoorskakelknoppie en 'n klokinvoer. Aan die ander kant is ons enkele uitset 'n bus LED -ligte wat ons straatligte verteenwoordig. Vir hierdie model het ons 'n scenario van 16 straatligte gebruik bloot omdat dit die maksimum aantal ingeboude LED -uitsette op die Basys 3 -bord is. Uiteindelik kon ons met behulp van hierdie diagram ons Vivado -projek-, bron- en beperkingslêers skep met gepaste insette en uitsette.

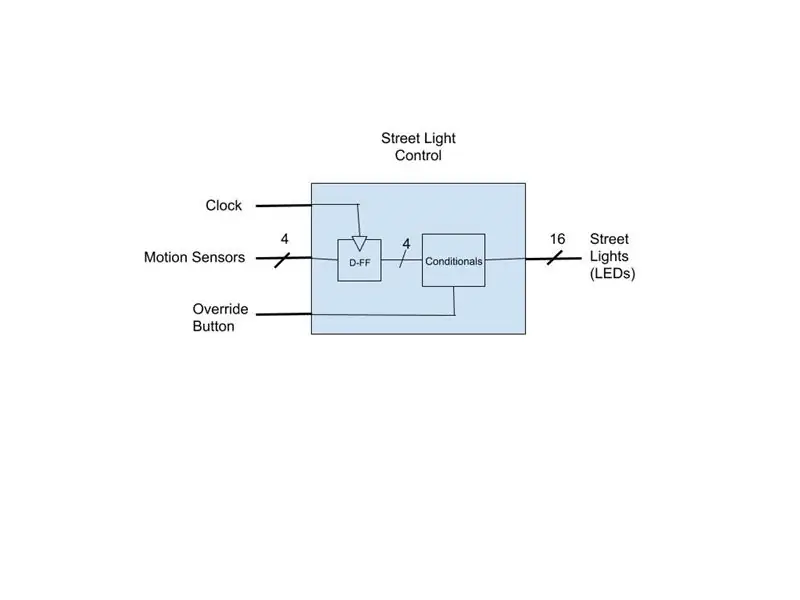

Stap 2: Komponente

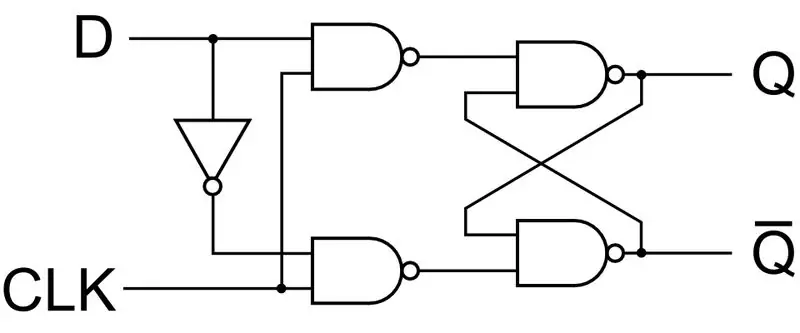

In hierdie stap ondersoek ons die komponente van ons swart boksdiagram. Ons eerste komponent is 'n VHDL-bronlêer wat D-flip-flops bevat. D flip-flops neem eenvoudig watter sein ook al vanaf die sensors op die horlosie se ingang na hulle toe, en hou die data vas tot die volgende stygende rand. Dit verhoed dat ons sensitiewe bewegingsensors veroorsaak dat die uitvoer -LED's "flikker". Ons plaas ook 'n enkele D-flip-flop op die ingangsein van die knoppie om LED's aan te hou vir ongeveer 5-7 sekondes nadat die knoppie gedruk is. Ons het dit ook deur 'n klokverdeler gehardloop.

entiteit clk_div2 is Port (clk: in std_logic; sclk: out std_logic); einde clk_div2;

argitektuur my_clk_div van clk_div2 is

konstante max_count: heelgetal: = (300000000); sein tmp_clk: std_logic: = '0'; begin my_div: proses (clk, tmp_clk) veranderlike div_cnt: heelgetal: = 0; begin as (rising_edge (clk)) dan as (div_cnt = MAX_COUNT) dan tmp_clk <= nie tmp_clk; div_cnt: = 0; anders div_cnt: = div_cnt + 1; eindig as; eindig as; sclk <= tmp_clk; beëindig proses my_div; eindig my_clk_div;

Ons laaste komponent in hierdie diagram is 'n gedrags -VHDL -bronlêer wat voorwaardes bevat vir die uitsette gebaseer op die opset van insetseine.

Stap 3: D flip-flops

Die vier flip-flops wat aan die insetseine geheg is, is noodsaaklik vir die funksionaliteit van ons stelsel. Soos voorheen gesê, met sensitiewe bewegingsensors en 'n oorheersingsknoppie, gebruik die flip-flops grendels om slegs ons insetsignaal op die stygende kant van die klok uit te voer. Hierdie opeenvolgende logika beteken dat ons straatligte 'n vaste tyd kan aanhou nadat dit deur 'n vinnige beweging veroorsaak is. Die kodering vir 'n D-Flip Flop is redelik eenvoudig:

beginproses (CLK) begin as rising_edge (CLK) dan Q <= D; eindig as; einde proses;

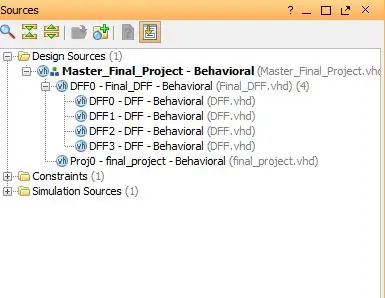

Die hele ding kan in 'n enkele if -verklaring saamgestel word. Sodra ons hierdie stuk gehad het, het ons 'n strukturele VHDL-bronlêer geskep wat al vier ons nodige flip-flops bevat:

begin DFF0: DFF -poortkaart (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF -poortkaart (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF -poortkaart (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF -poortkaart (CLK => CLK, D => D (3), Q => Q (3));

einde Gedrag;

Dit help om ons hoofstruktuurlêer te behou waar ons alle stelselkomponente baie meer skoon en georganiseerd bymekaarbring.

Stap 4: Voorwaardes

Om ons kode kompak en doeltreffend te hou, het ons al ons voorwaardes in 'n enkele verklaring geskryf. Vir ons afgeskaalde model het ons 16 moontlike LED -uitsetkonfigurasies gehad, aangesien elke bewegingsensor verantwoordelik is vir 'n groep van 4 LED's.:

geval NMS is wanneer "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED = = "1111111111111111"; eindsaak;

Stap 5: Beperkings

Om u insette en uitsette met behulp van Vivado behoorlik te kan verklaar, moet u 'n beperkingslêer implementeer met alle poorte, knoppies, LED's en horlosies wat gebruik word.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_port] PACK_ LED U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_ LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_port] 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDAARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11] }_OS_33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_propport IOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Stap 6: Hoofbronlêer

In hierdie hooflêer bring ons alle komponentbronlêers bymekaar wat voorheen genoem is. Hierdie lêer funksioneer as 'n strukturele kode wat die verskillende komponente bymekaarbring.

entiteit Master_Final_Project is Port (BTN: in STD_LOGIC; CLK: in STD_LOGIC; MS: in STD_LOGIC_VECTOR (3 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); einde Master_Final_Project;

argitektuur Gedrag van Master_Final_Project is

komponent final_project is Port (--CLK: in STD_LOGIC; NMS: in STD_LOGIC_VECTOR (3 downto 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 downto 0); LED: out STD_LOGIC_VECTOR (15 downto 0)); eindkomponent;

komponent Final_DFF is

Poort (CLK: in STD_LOGIC; D: in STD_LOGIC_Vector (3 af na 0); V: uit STD_LOGIC_Vector (3 af na 0)); eindkomponent;

sein DFF02proj30: STD_LOGIC;

sein DFF12proj74: STD_LOGIC; sein DFF22proj118: STD_LOGIC; sein DFF32proj1512: STD_LOGIC;

begin

DFF0: Final_DFF -poortkaart (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: final_project poortkaart (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); einde Gedrag;

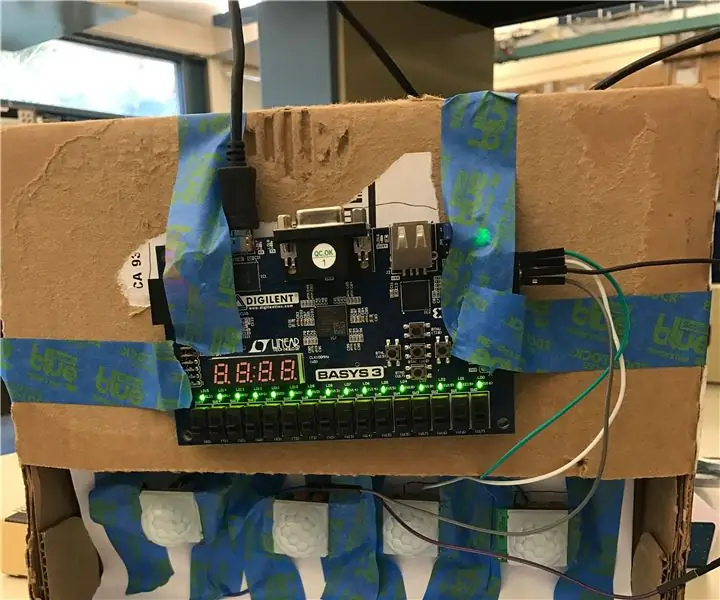

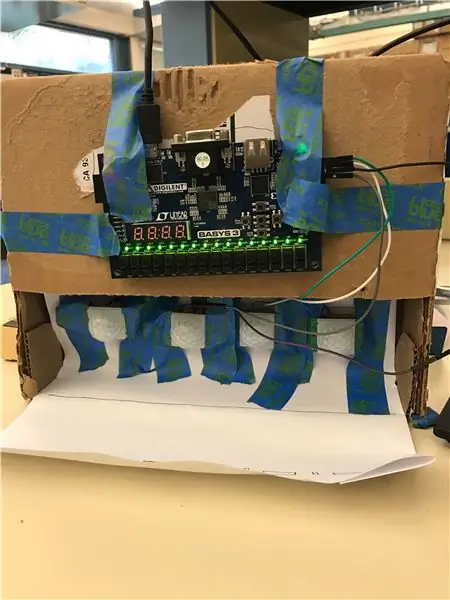

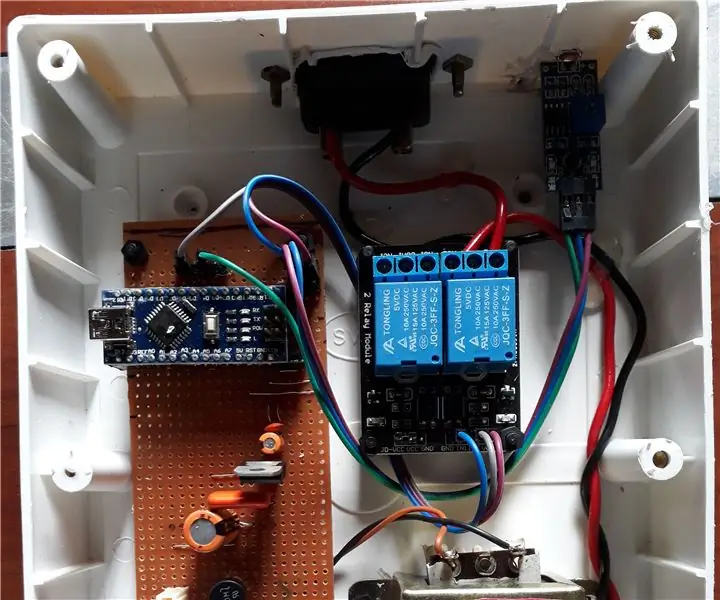

Stap 7: Montering

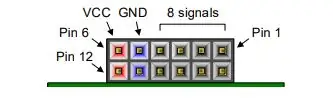

Die hardeware -samestelling vir hierdie projek is minimaal. Die enigste vereiste stukke is soos volg:

1. Basys 3 bord (1)

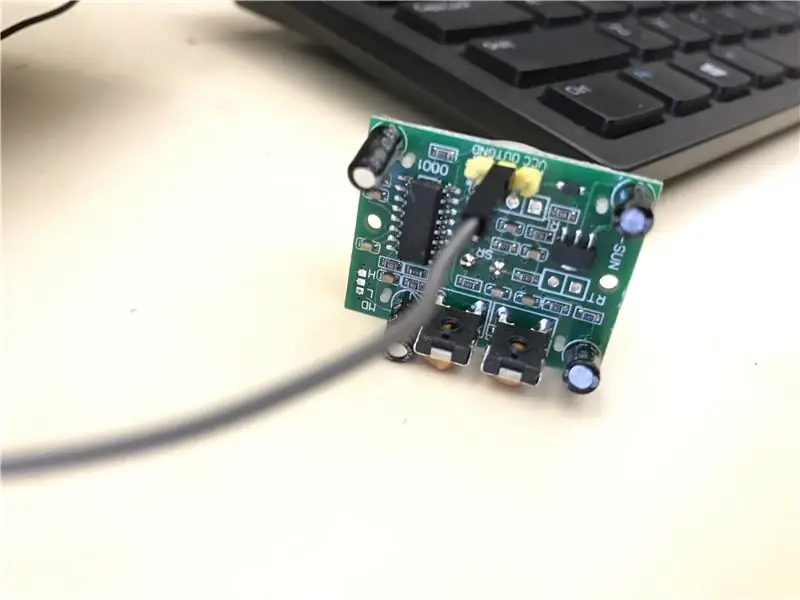

2. Goedkoop bewegingsensors wat hier op Amazon gevind kan word. (4)

3. Man-tot-vrou-leidrade (4)

Vergadering:

1. Koppel 4 manlike kabels aan PMod-kop JB-poorte 1-4 (sien figuur).

2. Koppel die vroulike ente aan die uitsetpen van elke bewegingsensor.

Stap 8: Laai die program

Nou is ons gereed om die VHDL -hoofbronlêer na die Basys 3 -bord te laai. Maak seker dat u sintese, implementering en bitstream -kontrole opdoen vir moontlike foute. As alles suksesvol werk, maak die hardeware bestuurder oop en programmeer die Basys 3 toestel. U projek is nou voltooi!

Aanbeveel:

Bewegings geaktiveerde cosplay -vleuels met behulp van Circuit Playground Express - Deel 1: 7 stappe (met foto's)

Motion Activated Cosplay Wings Using Circuit Playground Express - Deel 1: Dit is deel een van 'n tweedelige projek, waarin ek jou my proses vir die maak van 'n paar outomatiese sprookjesvlerke gaan wys. Die eerste deel van die projek is die meganika van die vlerke, en die tweede deel maak dit draagbaar en voeg die vlerke by

Bewegings geaktiveerde lampskakelaar: 3 stappe

Bewegings geaktiveerde lampskakelaar: wanneer ons ons lessenaar of kamer verlaat, vergeet ons meestal om die ligte daar af te skakel. Dit veroorsaak elektrisiteitsverlies en verhoog u elektrisiteitsrekening. Maar wat as die ligte outomaties afskakel nadat u die kamer verlaat het? Ja in

Bewegings geaktiveerde wagter: 5 stappe

Motion Activated Sentinel: " Hierdie instruksies is geskep ter voldoening aan die projekvereiste van die Makecourse aan die Universiteit van Suid -Florida (www.makecourse.com) " Hallo, my naam is Ruben Duque. 'N Student in meganiese ingenieurswese aan die Universiteit van Suid -Flor

Bewegings geaktiveerde ligskakelaar met ligsensor: 5 stappe

Bewegings geaktiveerde ligskakelaar met ligsensor: bewegings geaktiveerde ligskakelaar het baie toepassings, beide tuis en op kantoor. Dit het egter die voordeel dat dit 'n ligsensor bevat, sodat hierdie lig slegs in die nag geaktiveer kan word

Bewegings geaktiveerde trappe: 6 stappe (met foto's)

Bewegings geaktiveerde trappe: Ja, ek weet wat u dink, dit lyk effens oordrewe, maar in die eerste plek hoef u nooit weer bekommerd te wees oor die stomp nie, en in die tweede plek is dit so traag om op en af te trap. lekker, ek het myself boontoe gaan sonder rede