INHOUDSOPGAWE:

- Stap 1: Wat is Vivado HLS?

- Stap 2: HLS -videobiblioteek

- Stap 3: Sintetiseer

- Stap 4: Weergawe en ander inligting vir uitvoer

- Stap 5: Uitvoer na 'n Vivado IP -biblioteek

- Stap 6: Sintese en uitvoer analise

- Stap 7: Voeg die IP -biblioteek in Vivado by

- Stap 8: Opgradeer

- Stap 9: Bykomende besonderhede en inligting

- Stap 10: Uitset en invoer

- Stap 11: AXI Register Interfacing

- Stap 12: Dataflow Pragma

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:27.

- Laas verander 2025-01-23 12:53.

Wou u ooit real-time verwerking op video verwerk sonder om veel latensie of in 'n ingeboude stelsel by te voeg? FPGA's (veldprogrammeerbare hekskikkings) word soms gebruik om dit te doen; Om videoverwerkingsalgoritmes in hardeware -spesifikasietale soos VHDL of Verilog te skryf, is egter op sy beste frustrerend. Voer Vivado HLS in, die Xilinx -instrument waarmee u in 'n C ++ - omgewing kan programmeer en daaruit hardeware spesifikasies taalkode kan genereer.

Vereiste sagteware:

- Vivado HLS

- Vivado

- (As u die AXI -registers gebruik) Vivado SDK

(Opsioneel) Laai die Xilinx -voorbeelde hier af:

Xilinx HLS video voorbeelde

Stap 1: Wat is Vivado HLS?

Vivado HLS is 'n instrument wat gebruik word om c ++ kode in hardeware strukture te omskep wat op 'n FPGA geïmplementeer kan word. Dit bevat 'n IDE om hierdie ontwikkeling te doen. Sodra u die ontwikkeling van die kode vir HLS voltooi het, kan u u gegenereerde IP in 'n formaat uitvoer vir gebruik met Vivado.

Laai die aangehegte lêers af en plaas dit naby die plek waar u u projek gaan skep. (hernoem hulle terug na "top.cpp" en "top.h" as hulle 'n gerandomiseerde naam het)

Stap 2: HLS -videobiblioteek

Die HLS -videobiblioteek bevat dokumentasie met verwysingsontwerpe in hierdie vraestel: XAPP1167 'n Ander goeie bron is die Xilinx Wiki -bladsy daaroor.

Begin Vivado HLS.

Skep 'n nuwe projek.

Neem die lêers wat u in die vorige stap afgelaai het, en voeg dit as bronlêers by. (Let wel: die lêers word nie na die projek gekopieer nie, maar bly eerder waar dit is)

Gebruik dan die blaai -knoppie om die topfunksie te kies.

Kies die Xilinx -deel wat u gebruik op die volgende bladsy.

Stap 3: Sintetiseer

Oplossing => Begin C -sintese => Aktiewe oplossing

Na ~ 227.218 sekondes moet dit gedoen word. (Let wel: u werklike sintetietyd sal afhang van baie faktore)

Stap 4: Weergawe en ander inligting vir uitvoer

Weergawegetalle is in wisselwerking met Vivado, sodat u die IP in 'n ontwerp kan opdateer. As dit 'n geringe weergawe is, kan dit in plek wees, terwyl groot weergawes verander moet word om die nuwe blok handmatig in te voeg en die ou te verwyder. heeltemal outomaties gedoen deur op die update -knoppie te druk. U kan 'report_ip_status' in die Vivado tcl -konsole uitvoer om die status van u IP te sien.

Stel die weergawenommers en ander inligting in Oplossing => Oplossingsinstellings …

Alternatiewelik kan hierdie instellings tydens die uitvoer ingestel word.

Stap 5: Uitvoer na 'n Vivado IP -biblioteek

Oplossing => Voer RTL uit

As u nie die IP -biblioteekbesonderhede in die vorige stap gestel het nie, kan u dit nou doen.

Stap 6: Sintese en uitvoer analise

Op hierdie skerm kan ons die statistieke oor ons uitgevoerde module sien, wat toon dat dit aan ons kloktyd van 10ns (100MHz) voldoen en hoeveel van elke bron dit gebruik.

Met 'n kombinasie hiervan, ons sinteseverslag en ons dataflow -analise, kan ons sien dat dit 317338 kloksiklusse * 10ns klokperiode * 14 pypleidingfases = 0,04442732 sekondes neem. Dit beteken dat die totale latensie wat deur ons beeldverwerking bygevoeg word, minder as een twintigste sekonde is (as dit op die geteikende 100MHz geklok word).

Stap 7: Voeg die IP -biblioteek in Vivado by

Om u gesintetiseerde IP -blok te gebruik, moet u dit by Vivado voeg.

Voeg in Vivado 'n IP-bewaarplek by u projek deur na die IP-katalogus te gaan en met die rechtermuisknop "Add Repository …" te kies.

Gaan na u Vivado HLS -projekgids en kies u oplossingsgids.

Dit moet die IP wat dit gevind het, rapporteer.

Stap 8: Opgradeer

Soms moet u veranderinge aan u HLS -blok aanbring nadat u dit in 'n Vivado -ontwerp ingesluit het.

Om dit te kan doen, kan u die veranderings aanbring en die IP weer met 'n hoër weergawenommer herontwerp en uitvoer (sien besonderhede in die vorige stap oor groot/geringe weergawe -nommerveranderings).

Nadat u die nuwe weergawe uitgevoer het, verander u u IP -bewaarplekke in Vivado. Dit kan gedoen word as Vivado agterkom dat die IP in die bewaarplek verander het, of as dit handmatig geaktiveer word. (Let op: as u u IP -bewaarplekke herlaai nadat u begin het, maar voordat die uitvoer in HLS voltooi is, sal die IP tydelik nie daar wees nie, wag totdat dit klaar is en weer verfris.)

Op hierdie stadium moet 'n venster verskyn met die inligting dat 'n IP op die skyf verander is en u die opsie gee om dit op te dateer met 'n 'Upgrade Selected' knoppie. deur op die knoppie te druk, word die ou IP outomaties deur die nuwe vervang, anders kan meer werk nodig wees.

Stap 9: Bykomende besonderhede en inligting

Die volgende stappe bied meer inligting oor hoe HLS -sintese werk en wat u daarmee kan doen.

Sien hierdie instruksies vir 'n voorbeeld van 'n projek met 'n HLS -gesintetiseerde IP -blok.

Stap 10: Uitset en invoer

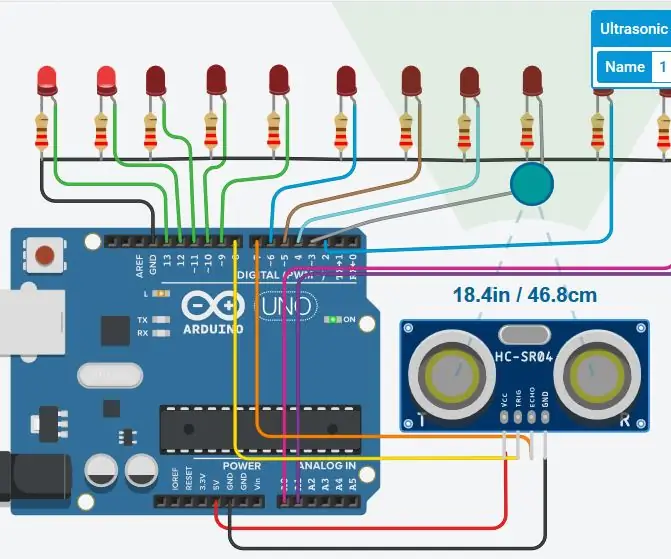

Uitsette en insette na die finale IP -blok word bepaal uit 'n analise wat die sintetiseerder doen van die vloei van data in en uit die topfunksie.

Net soos in VHDL of verilog, kan HLS u besonderhede spesifiseer oor die verbindings tussen IP. Hierdie reëls is voorbeelde hiervan:

leegte beeldfilter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE aspoort = video_in bundel = INPUT_STREAM #pragma HLS INTERFACE aspoort = video_uit bundel = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite poort = x bundel = CONTROL_BUS offset = 0x14 #pragma HLS INTERCONT = y

U kan sien hoe die hawens wat op die IP -blok vertoon word, beïnvloed word deur hierdie riglyne.

Stap 11: AXI Register Interfacing

Om die invoer/uitset van/na u IP -blok na die PS te kry, is 'n goeie manier om dit te doen deur middel van 'n AXI -koppelvlak.

U kan dit in u HLS -kode spesifiseer, insluitend die verrekenings wat gebruik moet word om later toegang tot die waarde te kry:

leegte beeldfilter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite poort = x bundel = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

As u eers behoorlik in Vivado gekoppel is, het u toegang tot die waardes met behulp van hierdie kode in Vivado SDK:

#sluit "parameters.h" in

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Hiermee eindig u met 42 in x en 0xdeadbeef in y

Stap 12: Dataflow Pragma

Binne die #pragma DATAFLOW verander die manier waarop die kode geïmplementeer word van normale C ++. Die kode word in die pyplyn geplaas sodat alle instruksies te alle tye in verskillende dele van die data uitgevoer word (dink aan dit soos 'n monteerbaan in 'n fabriek, elke stasie werk voortdurend met een funksie en stuur dit na die volgende stasie)

uit die beeld kan u sien dat elkeen van die voorskrifte

Alhoewel dit normale veranderlikes blyk te wees, word img -voorwerpe eintlik as klein buffers tussen die opdragte geïmplementeer. Deur 'n beeld as 'n invoer vir 'n funksie te gebruik, 'verbruik' dit en word dit nie meer bruikbaar nie. (Vandaar die behoefte aan die dubbele opdragte)

Aanbeveel:

UK Ring Video Doorbell Pro Werk met meganiese klokkie: 6 stappe (met foto's)

UK Ring Video Doorbell Pro werk met meganiese klokkie: *************************************** **************** Let asseblief daarop dat hierdie metode nou net met wisselstroom werk. Ek sal opdateer as/as ek 'n oplossing vind vir deurklokkies met DC -krag. aanbod, benodig u nie

Vídeo Tutoriales De Tecnologías Creativas 01: Hallo wêreld! Blink, Hacemos Parpadear Nuestro Primer Led Con Arduino: 4 stappe

Vídeo Tutoriales De Tecnologías Creativas 01: Hallo wêreld! Knippering, nuanses Nuestro Primer Led Con Arduino: 'n Eerstelike tutoriaal vir 'n vooraanstaande lid van 'n blik (knipper) en 'n diode LED met 'n Arduino Uno. Eiste eiencicio lo realizaremos mediante simulación and para ello utilizaremos Tinkercad Circuits (utilizando una cuenta gratuita)

Router word video -opnemer vir IP -kameras: 3 stappe

Router word video-opnemer vir IP-kameras: Sommige routers het 'n kragtige SVE en USB-poort op 'n bord en kan benewens routeringsfunksies ook as 'n video-opnemer gebruik word om video en klank te versamel en te versprei vanaf IP-kameras wat slegs stroom H264/265 RTSP (soos die meeste moderne goedkoop hi

Hoe om Vivado -simulasie te gebruik: 6 stappe

Hoe om Vivado Simluation te gebruik: Ek het hierdie simulasieprojek vir 'n aanlynklas gedoen. Die projek is geskryf deur Verilog. Ons sal simulasie in Vivado gebruik om die golfvorm in enable_sr (aktiveer syfer) te visualiseer van die stophorlosie -projek wat voorheen geskep is. Boonop sal ons

Camara De Video En Carro De Radio Control / Video Camera on R / C Truck: 5 Stappe

Camara De Video En Carro De Radio Control / Videokamera op R / C Truck: Este Instruccionable presentado en Espanol e Ingles.These Instructable aangebied in Spaans en Engels