INHOUDSOPGAWE:

- Stap 1: Blokdiagram

- Stap 2: Beginsel van werking

- Stap 3: Logiese implementering

- Stap 4: Oplossing van doodloopstraat

- Stap 5: Toestelkonfigurasie - Matrix0 -stroombaan

- Stap 6: Toestelkonfigurasie - SPI -kloklogika

- Stap 7: Toestelkonfigurasie - Eienskappe van Matrix0 -komponente

- Stap 8: Toestelkonfigurasie - Matrix1 -stroombaan

- Stap 9: Toestelkonfigurasie - 3 -bis binêre teller

- Stap 10: Toestelkonfigurasie - Vergelyk logika met 3 bisse

- Stap 11: Toestelkonfigurasie - Digitale vergelyk logika en tydelike register

- Stap 12: Toestelkonfigurasie - Eienskappe van Matrix1 -komponente

- Stap 13: Resultate

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:24.

- Laas verander 2025-01-23 12:53.

Beheerstelsels en verwante toestelle hanteer verskeie kragbronne, soos voorspellingslyne of batterye, en moet die hoogste (of die laagste) lyn tussen 'n gegewe stel volg.

Byvoorbeeld, laadskakeling in 'n stelsel met 'multi-battery', vereis dat die stelsel die minimum of die maksimum spanning tussen die batteryreeks monitor (maksimum of min as 'n funksie van die spesifieke skakelalgoritme) en die las dinamies na die die mees geskikte bron in reële tyd. Alternatiewelik moet die stelsel die laagste spanning battery tydelik ontkoppel vir die regte laai.

'N Ander voorbeeld is die moderne sonkragstelsel, waar elke sonpaneel toegerus is met 'n tiltrotaatmeganisme en 'n sonopsporingskring (laasgenoemde verskaf inligting oor die sonposisie om die paneel te oriënteer). Met die maksimumspanning-inligting kan elke posisie van die sonpaneel verfyn word op grond van die paneel van die snaar wat eintlik die hoogste uitsetspanning lewer, en sodoende 'n uitstekende vlak van kragoptimalisering bereik.

Daar is verskillende handelsmerke van kommersiële IC's (hoofsaaklik mikrobeheerders) wat in beginsel 'n maksimum -volger kan implementeer. Hulle benodig egter programmering en is minder koste-effektief as 'n oplossing met gemengde seine. Die aanvulling van 'n Dialog GreenPAKTM -ontwerp kan die bekostigbaarheid, grootte en modulariteit van die ontwerp positief beïnvloed. Hierdie ontwerp benut die voordeel om beide analoog en digitaal stroombane in een enkele chip te integreer.

In hierdie instruksies word die analoog voorkant en die digitale logika wat benodig word om 'n maksimum (of uiteindelik min) spanningszoeker tussen agt verskillende bronne te implementeer, geïmplementeer.

'N SLG46620G word gebruik om die 8-kanaal analoog maks/min spanningsmonitor te implementeer.

Hieronder beskryf ons die nodige stappe om te verstaan hoe die oplossing geprogrammeer is om die analoog maksimum/min spanningsmonitor van 8 kanale te skep. As u egter net die resultaat van die programmering wil kry, laai GreenPAK -sagteware af om die reeds voltooide GreenPAK -ontwerplêer te sien. Koppel die GreenPAK Development Kit aan op u rekenaar en klik op die program om die analoog maksimum/min spanningsmonitor van 8 kanale te skep.

Stap 1: Blokdiagram

Die figuur 1 toon die globale diagram van die geïmplementeerde stelsel.

'N String van tot 8 veranderlike spanningsbronne word gemultiplex en gekoppel aan 'n GreenPAK se ADC -module wat gekoppel is aan 'n pasgemaakte interne ontwerp wat die bron met die hoogste spanning ten opsigte van die ander kan kies. Die interne logika verskaf hierdie inligting vir vertoning of verdere verwerking.

Die ontwerp is gebaseer op die GreenPAK SLG46620G -produk, omdat dit al die nodige analoog en digitale boustene vir die toepassing insluit. In hierdie implementering word die skikking geskandeer deur middel van 'n analoog ADG508 analoog multiplexer wat direk deur die GreenPAK IC aangedryf word.

Die uitsetinligting is 'n 3-bis digitale nommer wat ooreenstem met die spanningsbronnommer by maksimum spanning. 'N Direkte manier om hierdie inligting te bekom, is om die nommer met 'n 7-segment-skerm te wys. Dit kan maklik bereik word deur die digitale uitset van die SLG46620G te koppel aan 'n 7-segment-skermbestuurder, soos die GreenPAK-oplossing beskryf in Reference of 'n gewone 74LS47 IC.

Die stroombaan wat aangebied word, soek na maksimum spanning. Om die ontwerp in 'n minimumspanningszoeker te omskep, moet 'n eenvoudige vooraf-kondisioneringskring tussen die analoog-multiplexer en die analoog GreenPAK-ingang bygevoeg word, wat die multiplexer-uitset van 'n 1 V-verwysingsspanning aftrek.

Stap 2: Beginsel van werking

Die ontwerp is daarop gemik om die bron met maksimum spanning te kies, daarom word 'n skandering op die hele skikking uitgevoer terwyl die laaste-maksimum waarde gestoor word en dit vergelyk word met die volgende insetwaarde (wat tot die volgende spanningsbron in die skandering behoort).

In die volgende sal ons na 'n volledige multiplex -ry langs al die insette verwys as 'n "scan" of "lus".

Vergelyking tussen twee waardes word nie verkry deur middel van ACMP -komponente nie (egter beskikbaar in die SLG46620G), maar eerder deur die DCMP -module, sodra die waardes onderskeidelik gedigitaliseer is. Dit is 'n gevorderde en verfynde tegniek wat die eerste keer in Reference bespreek is.

Figuur 2 toon hoe die SLG46620G vir hierdie ontwerp gestruktureer is.

Die analoog ingangsein gaan na die ADC-ingang deur die PGA-komponent met 'n stel versterking van 1. Verskeie versterkingsinstellings is ook moontlik om die beste pasmaat te vind met die voorkant-kondisioneringselektronika wat toegewy is aan die kartering van die insetspannings na die 0-1 V reeks van die GreenPAK ADC -module.

Die ADC werk in 'n enkelmodus en skakel die analoog sein om na 'n 8-bis digitale kode, wat dan na die DCMP-module oorgedra word. Die digitale kode word ook ingevoer in die SPI -blok, gekonfigureer as 'n ADC/FSM -buffer, waar 'n digitale kode gestoor kan word en nie verander totdat die volgende pols na die SPI CLK -invoer kom nie. Let op dat 'n toegewyde logika -blok die SPI CLK -invoer dryf. Ons sal hierdie deel later ondersoek, aangesien dit die 'kern' logika is wat verantwoordelik is vir die korrekte werking. 'N Nuwe digitale kode word slegs in die SPI -module gestoor as dit by die werklike maksimum ingangsspanning behoort.

Die DCMP -komponent word gebruik om huidige ADC -data te vergelyk met die laaste wenner (dit is die laaste maksimum gevind) wat in die SPI -blok gestoor is. Dit sal 'n pols genereer by die OUT+ -uitset wanneer nuwe ADC -data groter is as die vorige. Ons gebruik die OUT+ sein om die SPI -blok by te werk met die nuwe wenner.

'N Globale kloksein dryf ADC -omskakelings en algemene tydsberekeninge aan. Sodra 'n omskakeling uitgevoer is, polseer die ADC se INT -uitgangsein, betyds gekoördineer met die ADC parallelle data -uitset. Ons gebruik die INT-uitset ook om 'n 3-bis binêre teller te verhoog, geïmplementeer deur DFF's in Matrix1, wat om drie redes nuttig is:

1. Die telleruitganglyne spreek die eksterne analoog multiplexer aan, en bedien dus die volgende insetspanning aan die ADC;

2. Die telling word gevries in 'n 3-bis register (geïmplementeer in Matrix1) om die tydelike wenner tydens 'n skandering te stoor;

3. Die telling word gedekodeer om 'n tweede 3-bis-register (geïmplementeer in Matrix0) by te werk sodra 'n skandering voltooi is.

Stap 3: Logiese implementering

Die ADC -module bied agtereenvolgens onbepaalde tyd omgeskakel data van al die insetspannings, een na die ander. Sodra die multiplexer 0b111 (desimaal 7) aangespreek is, rol die toonbank na 0b000 (desimale 0) en begin 'n nuwe skandering van die insetspannings.

Tydens die skandering word die ADC INT -uitsetsein gegenereer wanneer die parallelle data -uitset geldig is. As hierdie sein pols, moet die analoog multiplexer oorskakel na die volgende ingang, wat die ooreenstemmende spanning aan die PGA verskaf. Daarom is die ADC INT-uitset die direkte kloksignaal van die 3-bis binêre teller van figuur 2, waarvan die 3-bis parallelle uitsetwoord die eksterne analoog multiplexer direk aanspreek ("V select" in figuur 1).

Kom ons verwys nou na 'n voorbeeld waar die ingangsspannings veronderstel is om die volgende verwantskappe te hê:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Figuur 3 verteenwoordig die belangrikste seine wat betrokke is by die maksimum-besluitmeganisme.

Aangesien data uiteindelik sinchronies met INT -pulse in die SPI -bufferregister ingeskakel word, bestaan daar 'n vergelykingsvenster waar die SPI -bufferinhoud vergelyk word met die volgende ADC -omskakelingsresultaat. Hierdie spesifieke tydsberekening lei tot die opwekking van OUT+ pulse by die DCMP -uitset. Ons kan van hierdie pulse gebruik maak om nuwe waardes in die SPI -bufferregister te laai.

Soos blyk uit die SPI -bufferdatalyn van die vorige figuur, bevat die SPI -register altyd die grootste waarde onder die 8 insette, en dit word slegs bygewerk wanneer 'n groter waarde deur die DCMP -module opgespoor word (verwys na die DCMP OUT+ uitsetlyn van die plot, die ontbrekende pulse veroorsaak dat V2 in die register geblokkeer bly totdat dit vergelyk word met V5).

Stap 4: Oplossing van doodloopstraat

As die geïmplementeerde logika net soos hierbo beskryf is, is dit duidelik dat ons in 'n dooie punt kan beland: die stelsel kan slegs spannings hoër opspoor as die wat ooreenstem met wat in die SPI -bufferregister gestoor is.

Dit is ook geldig indien hierdie spanning sou afneem en dan 'n ander inset, tot nou laer as dit, die hoogste word: dit sal nooit opgespoor word nie. duidelikheid.

Ten tyde van herhaling 2 daal V3 en V1 is die werklike maksimum spanning. Maar die DCMP -module bied nie 'n polsslag nie, omdat die data wat in die SPI -bufferregister gestoor is (wat ooreenstem met 0,6 V) groter is as die wat ooreenstem met V1 (0,4 V).

Die stelsel gedra hom dan as 'n 'absolute' maksimum finder en werk die uitvoer nie korrek op nie.

'N Goeie manier om hierdie probleem op te los, is om die data te herlaai in die SPI -bufferregister wanneer die stelsel 'n volledige peilingsiklus van alle kanale voltooi.

Trouens, as die spanning op die ingang nog steeds die hoogste is, verander niks nie en gaan die beheer veilig voort (verwys na figuur 4 hierbo, dit is die geval van Loop Iterations 0 en 1). Aan die ander kant, as die spanning by die ingang toevallig daal tot 'n waarde wat minder is as 'n ander ingang, gee die herlaai van die waarde die DCMP -module die moontlikheid om 'n OUT+ -puls te lewer wanneer dit met die nuwe maksimum waarde vergelyk word (dit is die geval van Loop Iterations 2 en 3).

'N Stukkie logiese kring is nodig om die probleem te oorkom. Dit moet 'n kloksignaal na die SPI-komponent genereer wanneer die lus die werklike maksimum inset bereik, en sodoende 'n herlaai van sy bygewerkte datawoord in die SPI-bufferregister dwing. Dit sal in afdeling 7.2 en 7.6 hieronder bespreek word.

Stap 5: Toestelkonfigurasie - Matrix0 -stroombaan

Die SLG46620G het twee Matrix -blokke, soos uitgebeeld in Figuur 2. Die volgende figure toon die onderskeie apparaatkonfigurasies.

Die boonste gedeelte van die kring is die 'lusregister' wat met 3 DFF's (DFF0, DFF1 en DFF2) gerealiseer is. Dit word verfris na elke lus van die ingangsmultiplekser om die binêre nommer van die "wenner", dit is die inset met die hoogste spanning in die laaste skandering, aan 'n 7-segment-skermbestuurder te stuur. Beide die klok na die DFF's en die data kom uit die logika wat in Matrix1 geïmplementeer word, onderskeidelik deur poort P12, P13, P14 en P15.

Die onderste deel is die analoog voorkant met ingang by Pin 8 en PGA met versterking x1. Die ADC INT -uitset gaan beide na die logika van SPI en na Matrix1 via poort P0, waar dit sal dien as die kloksein vir die geïmplementeerde teller.

ADC- en SPI -parallelle data -uitsette word onderskeidelik NET11 en NET15 gemerk om aan die DCMP -komponent in Matrix1 gekoppel te word.

Stap 6: Toestelkonfigurasie - SPI -kloklogika

Soos vroeër in die afdeling "Logiese implementering" aangedui, word die SPI -bufferregister bygewerk elke keer dat 'n vergelyking tussen die werklike gestoorde waarde en die nuwe ADC -omskakelingsdata 'n puls genereer by die DCMP OUT+ -uitgang.

Seinintegriteit word verseker as hierdie sein EN-gerig is met die ADC INT-uitset. Dit vermy enige piek en valse sneller.

Ons het ook onderstreep dat die SPI -buffer opgedateer moet word wanneer die lus die werklike data van die wenner bereik om die dooie situasies te vermy.

Drie seine is dan in die spel vir die regte SPI -klok:

1. ADC INT-uitset (LUT0-IN1)

2. DCMP OUT+ uitset (LUT0-IN0 via poort P10)

3. Tel is gelyk aan Klinksein (LUT0-IN2 via poort P11)

Die eerste twee is AND-ed en albei OF-ed met laasgenoemde in LUT0, waarvan die implementering soos in Figuur 6 gekonfigureer is.

Stap 7: Toestelkonfigurasie - Eienskappe van Matrix0 -komponente

Die figure 7-10 toon die oorblywende komponente-eiendomsvensters wat aan Matrix0 behoort.

Stap 8: Toestelkonfigurasie - Matrix1 -stroombaan

Stap 9: Toestelkonfigurasie - 3 -bis binêre teller

Die boonste gedeelte van die kring bevat logiese elemente, hoofsaaklik 'n 3-bis binêre teller wat deur die ADC INT-uitset geklok word, soos reeds bespreek. Hierdie teller is geïmplementeer met 'n redelik 'standaard' skematiese figuur in figuur 12.

Hierdie toonbank word in ons ontwerp gerealiseer deur middel van flip-flops DFF9, DFF10, DFF11 en INV1, LUT4, LUT8. Die DFF9 -uitset is die LSB, terwyl DFF11 die MSB is soos getoon in figuur 13.

LUT4 is as 'n XOR gekonfigureer terwyl LUT8 die AND-XOR logika van figuur 12 uitvoer.

Telleruitgange gaan na drie digitale uitsetpenne om die eksterne analoog -multiplexer aan te spreek.

LUT10 dekodeer die toonbank se kode wanneer 'n skandering voltooi is en voer 'n pols na Matrix0 via DLY8 en poort P12. Dit word eenvoudig bewerkstellig deur die uitsette van die toonbank te ANDERE en sodoende nommer 7 dec (0b111 binêre, einde van lus) te ontsyfer.

Stap 10: Toestelkonfigurasie - Vergelyk logika met 3 bisse

Figuur 15 toon die stroombaan wat gebruik word om op te spoor wanneer die lus herhaal na die huidige "wenner" -adres. In hierdie geval, soos reeds bespreek, moet 'n digitale puls 'n herlaai van die huidige ADC-resultaat dwing om 'n moontlike dooie punt op te los.

Die "wenner" -adres word in die tydelike register van Matrix1 gestoor (sien hieronder), terwyl die huidige adres deur die binêre teller afgelewer word.

XNOR -hekke bied 'n ware (logiese 1 of 'hoë') uitset wanneer beide insette gelyk is. EN deur hierdie sein vir alle bisse (LUT9) in te gee, gee ons 'n polsslag as beide binêre kodes dieselfde is. Besonderhede oor XOR -hekke as 'n pariteitskontroleerder kan gevind word in Reference.

Die sein 'Counter-equals-Latch' word via poort P11 na Matrix0 gestuur.

Stap 11: Toestelkonfigurasie - Digitale vergelyk logika en tydelike register

Die onderste gedeelte van Figuur 11 (gemerk in Figuur 16) toon die DCMP-blok, die besluitnemende deel van hierdie ontwerp.

DFF6, 7 en 8 vorm 'n 3-bis register om die tydelike invoernommer "wenner" te stoor terwyl die lus loop. Toevoer tot die flip-flops is die 3-bis binêre telleruitsette, soos sigbaar in die globale Matrix1-stroombaan in figuur 11, hier ter wille van duidelikheid oorgeslaan.

Uitsette van hierdie register kan die 7-segment-skerm nie direk dryf nie, want die waarde wat hier gestoor word, verander tydens 'n skandering en moet slegs as 'geldig' beskou word aan die einde van die skandering self.

Om hierdie rede maak die tydelike registeruitsette verbinding met die Matrix0 se lusregister via intermatriks-poorte P13, P14 en P15.

Dit is belangrik om in figuur 16 op te let dat die tydelike register deur die DCMP OUT+ -uitgang geklok word as die vergelyking van die ADC-SPI-register 'n nuwe maksimum vind.

Dieselfde OUT+ sein word oorgedra na Matrix0, SPI CLK Logic, via poort P10.

Stap 12: Toestelkonfigurasie - Eienskappe van Matrix1 -komponente

Die figure 17-19 toon die komponente-eiendomsvensters van Matrix1.

Stap 13: Resultate

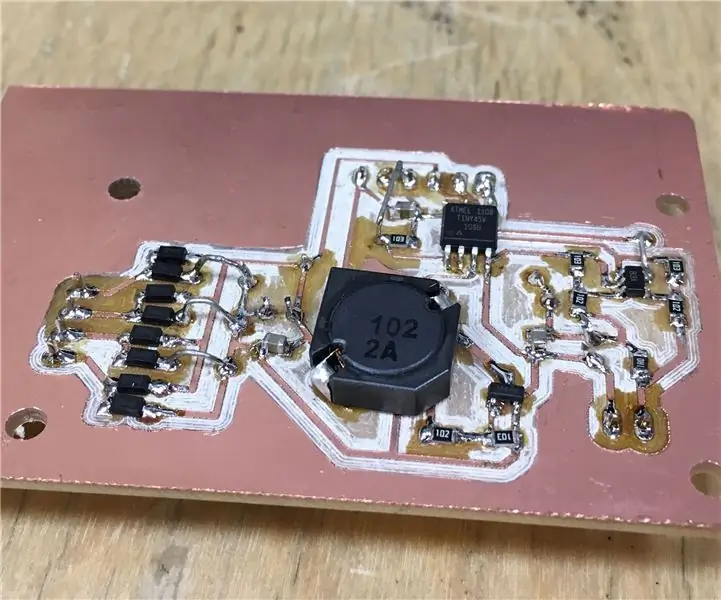

Om die implementering te toets, is 'n evalueringsbord -prototipe saamgestel, waar die 8 analoog ingangsspannings verkry word deur 'n reeks weerstandsverdelers met TrimPots (soos getoon in figuur 20).

Die multiplexer wat gebruik word, is 'n ADG508, 'n onderdeel wat met 'n enkele voeding (12 V) kan werk.

Die 7-segment vertoonbestuurder is 'n 74LS47. Dit dekodeer 'n parallelle invoerwoord en dryf direk 'n 7-segment-skerm met 'n gewone anode aan.

Die evalueringsbord het 'n 2x10 reghoekige aansluiting om direk aan te sluit by 'n GreenPAK Advanced Development Platform by sy uitbreidingskoppelstuk soos in Figuur 21 getoon.

Die samewerking met die GreenPAK Advanced Development Platform maak dit baie eenvoudig om die seine te meet vir 'n vinnige ondersoek. Figuur 22 toon byvoorbeeld 'n stel seine (onderskeidelik CLOCK, ADC INT output, en DCMP OUT+ output) soos vasgelê deur 'n HP 54620A Logic Analyzer. Golfvorme word veroorsaak deur 'n stygende rand van OUT+ sein (op die omvang gemerk as 'A> B'), daarom is dit 'n golfvormopname wanneer 'n nuwe maksimum spanning tussen die analoog insette bespeur word. Dit is eintlik verkry deur een van die TrimPots van die Evalueringsbord te draai om die ooreenstemmende spanning wat in Figuur 22 getoon word, te verhoog.

Figuur 23 toon die skema van die Evalueringsraad.

Afsluiting

In hierdie instruksies het ons 'n maksimum (of min) spanningszoeker van agt kanale geïmplementeer om as 'n algemene toevoeging tot meerkanaals beheerstelsels gebruik te word. Die aangebied benadering benut gevorderde funksies van die GreenPAK -komponente en toon aan hoe dit moontlik is om in een enkele chip analoog en digitale funksies te integreer. Verskeie kommersiële IC's kan met Dialog GreenPAK's vervang word, sodat die grootte en koste van die aansoek verminder kan word.

Aanbeveel:

Spanningsmonitor vir hoogspanningsbatterye: 3 stappe (met foto's)

Spanningsmonitor vir hoogspanningsbatterye: In hierdie gids sal ek u verduidelik hoe ek my batteryspanningsmonitor vir my elektriese longboard gebou het. Monteer dit net soos u wil en verbind slegs twee drade aan u battery (Gnd en Vcc). Hierdie gids veronderstel dat u batteryspanning 30 volt oorskry, w

Maksimum kragpunttracker vir klein windturbines: 8 stappe

Maksimum Power Point Tracker vir klein windturbines: Daar is baie DIY windturbines op die internet, maar baie min verduidelik die resultaat wat hulle kry in terme van krag of energie. Daar is ook dikwels 'n verwarring tussen krag, spanning en stroom. Baie tyd sê mense: " ek meet

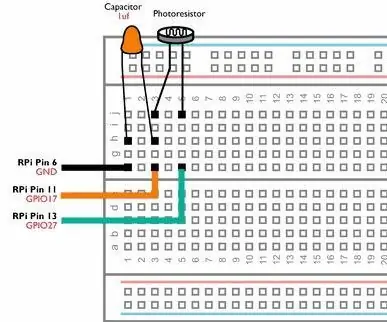

Raspberry Pi GPIO -kringe: Die gebruik van 'n LDR analoog sensor sonder 'n ADC (analoog na digitaal omskakelaar): 4 stappe

Raspberry Pi GPIO -kringe: Die gebruik van 'n LDR analoog sensor sonder 'n ADC (analoog na digitale omskakelaar): In ons vorige instruksies het ons u gewys hoe u die GPIO -penne van u framboos Pi aan LED's en skakelaars kan koppel en hoe die GPIO -penne hoog kan wees of Laag. Maar wat as u u Raspberry Pi met 'n analoog sensor wil gebruik? As ons 'n

Batteryoorplanting, herwinning tot die maksimum: 5 stappe

Batteryoorplanting, herwinning tot die maksimum: Tydens die skoonmaak van my werkswinkel het ek 'n paar DeWALT -batterye gevind wat heeltemal dood was. Hulle sou nie 'n aanklag neem nie, en om dit met hoë spanning te zap, werk nie eter nie. Aangesien die meeste van my gereedskap DeWALT is, is dit nuttig om ekstra batterye te gebruik

Picaxe -gebaseerde digitale termometer met maksimum en min: 13 stappe

Picaxe-gebaseerde digitale termometer met maksimum en min: (laat 'n boodskap, maar moenie te krities wees nie; dit is my eerste instruksie !!) Dit is 'n termometer wat ek vir ons kampeerwa gemaak het om die buitentemperatuur aan te toon. Dit is gebaseer op 'n Picaxe -chip, aangesien dit goedkoop en maklik is om te gebruik. As dit vir