INHOUDSOPGAWE:

- Stap 1: Bou 'n PWM-module- Bronlêer

- Stap 2: Bou 'n PWM-module- Vivado-opstelling

- Stap 3: Bou 'n PWM-module- Skep 'n projeklêer

- Stap 4: Bou 'n PWM-module- Blokontwerp en beperking van lêeropstelling (I)

- Stap 5: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (II)

- Stap 6: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (III)

- Stap 7: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (IV)

- Stap 8: Bou 'n PWM-module- Blokontwerp en beperking van lêeropstelling (V)

- Stap 9: Bou 'n PWM-module- hardeware-installasie

- Stap 10: Bou 'n PWM-module- Genereer Bitstream en begin SDK

- Stap 11: Bou 'n PWM-module- Skep 'n nuwe toepassing in Xilinx SDK

- Stap 12: Bou van 'n PWM-module- Oorsig van die Project Explorer (I)

- Stap 13: Bou van 'n PWM-module- Oorsig van die Project Explorer (II)

- Stap 14: Bou van 'n PWM-module- Oorsig van die Project Explorer (III)

- Stap 15: Bou van 'n PWM-module- Sluit PWM-funksie af (I)

- Stap 16: Bou van 'n PWM-module- Sluit PWM-funksie af (II)

- Stap 17: Bou van 'n PWM-module- Sluit PWM-funksie af (III)

- Stap 18: Bou 'n PWM-module- laat dit loop

- Stap 19: Stroom van videoverwerking op Digilent ZYBO met OV7670

- Stap 20: Voltooi blokdiagram

- Stap 21: Koppel die OV7670 aan die ZYBO

- Stap 22: Skep blokontwerp

- Stap 23: Voeg VHDL -lêers by vir OV7670 -kamerabeheer en -opname

- Stap 24: Voeg beperkingslêer by

- Stap 25: Voeg IP Repo by vir HLS IP

- Stap 26: Voeg modules en IP by

- Stap 27: IP -konfigurasie -instellings

- Stap 28: Voeg PS IP -blok by en konfigureer dit

- Stap 29: Deel 1. Bou 'n PWM -module vir Servomotors

- Stap 30: Sy -aansluitings vir video -invoer (aclk gemerk)

- Stap 31: Verbindings met OV7670

- Stap 32: Verbindings aan die buitekant van die video

- Stap 33: Begin blok- en verbindingsautomatisering

- Stap 34: Genereer HDL Wrapper

- Stap 35: Genereer Bitstream, voer hardeware uit na SDK, begin SDK vanaf Vivado

- Stap 36: SDK (geen FreeRTOS)

- Stap 37: FreeRTOS -implementering

- Stap 38: Gebruiksinstruksies

- Stap 39: Verwysings en skakels

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:27.

- Laas verander 2025-01-23 12:53.

Begin by stap een vir meer inligting oor die skep van 'n 2-as servo PWM-beheerder.

Begin by die massiewe blokdiagram (Stap 19) vir die volledige projek.

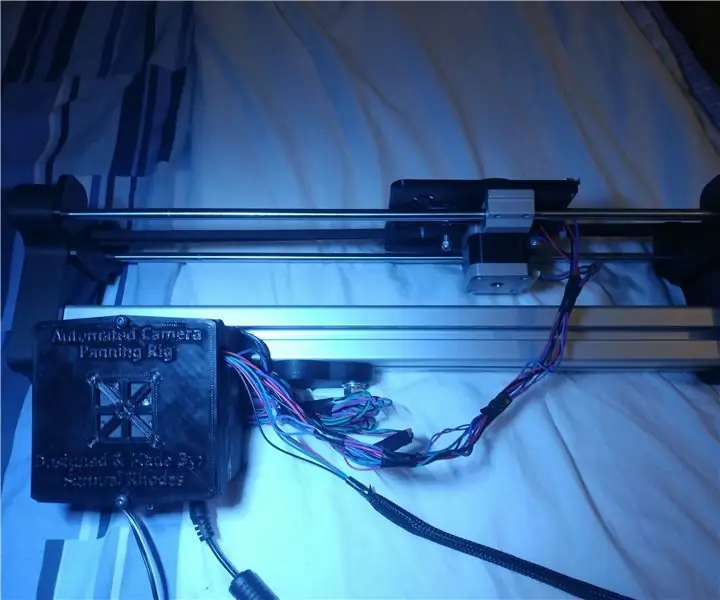

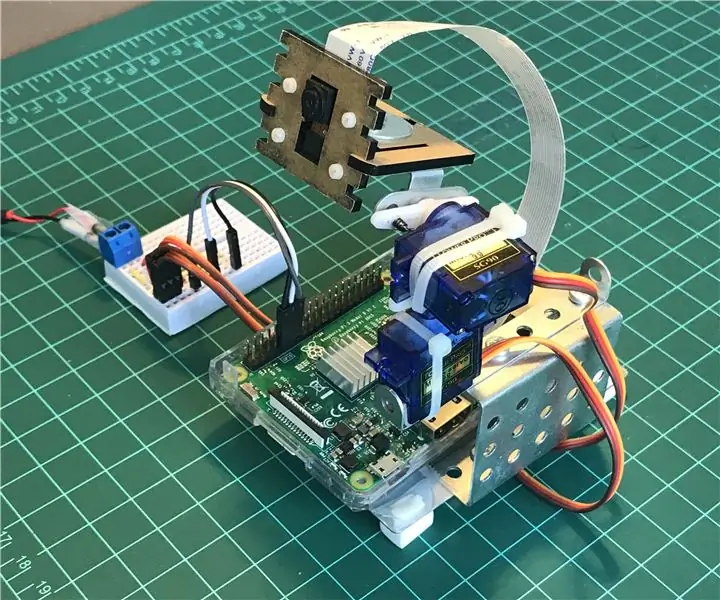

Opstelling van kamera + pan/kantel wat ons gebruik het:

Die PmodCON3 van Digilent is gebruik om die servo's aan te sluit.

Stap 1: Bou 'n PWM-module- Bronlêer

Stap 2: Bou 'n PWM-module- Vivado-opstelling

Laai eers die Vivado Design Suite From Xilinx -webwerf af. Installeer al die ontwerppakkette, insluitend Vivado Software Development Kit (SDK). Hierdie projek gebruik die weergawe 2017.2.

Intussen moet Digilent Adept 2 ook as 'n Zybo -bestuurder geïnstalleer word.

Stap 3: Bou 'n PWM-module- Skep 'n projeklêer

Voordat u 'n projeklêer skep, moet u seker maak dat u die Zybo -lêer reeds behoorlik geïnstalleer het as die tutoriaal hier:

Vivado Weergawe 2015.1 en latere bordlêerinstallasie

Open Vivado 2017.2. Klik op 'n vinnige begin op Skep projek -> Volgende -> Projeknaam (noem u projeknaam hier) -> Projek tipe. Kies op Projektipe RTL -projek en merk op "Moenie bronne spesifiseer nie". Kies dan vir die standaarddeel 'Boards' en 'Zybo' as vertoonnaam. Klik vervolgens op Voltooi om die projek te begin.

Stap 4: Bou 'n PWM-module- Blokontwerp en beperking van lêeropstelling (I)

Klik op Flow Navigator op "" Create Block Design "en druk dan op OK. klik op die "+" teken om die nodige IP's by te voeg. Voeg by:

- Een ZYNQ7 -verwerkingstelsel Twee AXI -timer

- Twee AXI -timer

Stap 5: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (II)

Nadat u IP's bygevoeg het, voer Block Automation en outomatiese verbinding uit. Sodra die outomatisering voltooi is, klik met die rechtermuisknop op die blok "axi_timer_0" op pwm0 -> Maak ekstern. Noem die eksterne pwm0 -pen as pwm_Xaxis. Herhaal ook die bogenoemde proses op die blok "axi_timer_1" en noem die eksterne pwm0 -pen as pwm_Zaxis.

Stap 6: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (III)

Let op dat ons elke keer as ons die Block Design in Vivado voltooi het, 'n HDL Wrapper moet maak. Aangesien dit die module op die hoogste vlak vir elke projek sal wees.

Stap 7: Bou van 'n PWM-module- Blokontwerp en beperking van lêeropstelling (IV)

Nou moet ons ons beperkingslêer opstel om penne wat aan ons blokdiagram gekoppel is, toe te ken. Sluit die venster Blokontwerp, op die oortjie Bronne, "Voeg bronne by"-> Voeg of skep beperkings-> voeg die Zybo-Master.xdc by as ons beperkingslêers.

Stap 8: Bou 'n PWM-module- Blokontwerp en beperking van lêeropstelling (V)

Maak die beperkingslêer Zybo-Master.xdc oop in die gids Constraints, los die poorte wat ons wil spesifiseer as uitvoerseine, en hernoem die naam "get_ports {XXXX}", wat XXXX die eksterne pen aandui in die blokdiagram. Die instelling van die beperkingslêer word in die figuur getoon.

Stap 9: Bou 'n PWM-module- hardeware-installasie

Koppel die servomotors aan die Pmod CON3. TowerPro SG90 is die servomotormodel wat ons in hierdie projek gebruik het. Vir die servomotordrade verteenwoordig die oranje draad die PWM -sein, gekoppel aan die SIG -pen in Pmod CON3. Die rooi draad Vcc is 'n kragdraad wat gekoppel is aan 'n VS -pen in Pmod CON3. Uiteindelik is die bruin draad Gnd 'n gronddraad wat aan die GND -pen gekoppel is. Plaas vervolgens die Pmod CON3 in die boonste ry van die JD -poort in die Zybo Board.

Stap 10: Bou 'n PWM-module- Genereer Bitstream en begin SDK

1. Begin Generate BitStream in die oortjie Project Navigator.

2. Voer hardeware uit: Lêer> Uitvoer> Uitvoer hardeware-> merk op 'sluit bitstroom in'-> OK 3. Begin SDK: Lêer-> Begin SDK.

Stap 11: Bou 'n PWM-module- Skep 'n nuwe toepassing in Xilinx SDK

Skep 'n nuwe toepassing:

Lêer> Nuut> Toepassingsprojek -> Voer die naam van u projek in -> Voltooi

Onder Project Explorer behoort daar drie vouers te wees.

In hierdie geval is “design_1_wrapper_hw_platform_0” die vouer wat Vivado voorheen uitgevoer het. Axis_2_PWM_SDK_bsp is die gids vir ondersteuningspakkette. En Axis_2_PWM_SDK is ons belangrikste projekmap in SDK. U kan 'helloworld.c' -lêer sien onder die 'src' -lêergids van Axis_2_PWM_SDK, waar' helloworld.c 'die hooflêer is.

Stap 12: Bou van 'n PWM-module- Oorsig van die Project Explorer (I)

Kom ons kyk na 'n paar lêers onder Project Explorer. Maak eers die "system.hdf" oop in die gids "design_1_wrapper_hw_platform_0". Hierdie lêer toon die adreskaart vir verwerker ps7_cortex9 en die IP -blokke wat in ons ontwerp voorkom.

Stap 13: Bou van 'n PWM-module- Oorsig van die Project Explorer (II)

Gaan dan die lêer "insluit" en "libsrc" na onder die "Axis_2_PWM_SDK_bsp" lêer. Biblioteeklêers hier stel ons in staat om met hardeware -randapparatuur te kommunikeer sonder om registers te speel.

Stap 14: Bou van 'n PWM-module- Oorsig van die Project Explorer (III)

Deur die BSP -dokumentasie word xtmrctr.h gevind as 'n Xilinx Timer Control Library wat verband hou met AXI Timer. Gewoonlik kan ons die gewenste PWM -funksie hier vind. As u egter die dokumentasie "tmrctr_v4_3" lees, toon dit dat die bestuurder tans nie die PWM -werking van die toestel ondersteun nie. Weens die tekort aan PWM -funksie, moet ons ons PWM -funksie afrond met behulp van xtmrctr.h en AXI Timer v2.0 LogiCORE IP -produkgids.

Stap 15: Bou van 'n PWM-module- Sluit PWM-funksie af (I)

Terug na die hooflêer "helloworld.c", bevat die volgende koplêers:

Stap 16: Bou van 'n PWM-module- Sluit PWM-funksie af (II)

Definieer die basisadresse van twee AXI TImer deur "xparameters.h".

Stap 17: Bou van 'n PWM-module- Sluit PWM-funksie af (III)

Bou die gewenste PWM -funksie.

Duty_val: skakel die graadwaarde om in duty cycle. PWM_Freq_Duty: stel die gewenste frekwensie en dienssiklus in om PWM te genereer. Die tydsduur moet ook toegeken word.

PWM_START: ken die PWM -registeradres toe en begin om PWM te genereer.

PWM_STOP: ken die PWM -registeradres toe en stop met die opwekking van PWM.

Die res van die demo -kode word getoon in "helloworld.c" onder "Axis_2_PWM_SDK"

Stap 18: Bou 'n PWM-module- laat dit loop

1. Programmeer die FPGA deur middel van SDK

- Koppel die Zybo Board via die USB -poort aan die rekenaar.

- Xilinx Tools -> Program FPGA

2. Begin die program

Klik op die "Run" -ikoon en maak die menu oop -> Run As -> Launch on Hardware

3. SDK Terminal

- Maak die SDK -terminale oop -> Koppel aan die seriële poort -> OK

- Begin die program. As die demokode suksesvol loop, moet u 'Inisialisering gedoen!' op die SDK Terminal.

Stap 19: Stroom van videoverwerking op Digilent ZYBO met OV7670

Volledige argieflêer aangeheg.

Stap 20: Voltooi blokdiagram

Dit toon die volledige diagram van alle verbindings en IP -blokke in die projek

Stap 21: Koppel die OV7670 aan die ZYBO

Maak 'n verbinding om die ov7670 -module na die ZYBO Pmods te dra

Data Pmod is Pmod D

Beheer Pmod is Pmod C

Koppel ook die PmodCON3 en servo's soos gespesifiseer in die eerste helfte van hierdie tutoriaal

Stap 22: Skep blokontwerp

Klik in Flow Navigator op "Create Block Design" en druk dan OK.

Stap 23: Voeg VHDL -lêers by vir OV7670 -kamerabeheer en -opname

Voeg die VHDL -lêers wat by hierdie stap aangeheg is, by die projek

Stap 24: Voeg beperkingslêer by

Voeg die aangehegte beperkingslêer by u projek.

Stap 25: Voeg IP Repo by vir HLS IP

Pak die aangehegte zip -lêer uit en pak dit uit in 'n nuwe gids met dieselfde naam in 'n nuwe gids (gids) genaamd "HLS_repo".

Voeg 'n IP-bewaarplek by u projek deur na die IP-katalogus te gaan, en klik met die rechtermuisknop "Add Repository …"

Gaan na u "HLS_repo" -gids en kies dit.

Opsioneel: Skep self die HLS -videoverwerkingsblok!

Stap 26: Voeg modules en IP by

Voeg die ov7670_axi_stream_capture-, debounce- en ov7670_controller -modules by die blokdiagram deur met die rechtermuisknop op die agtergrond te klik en "Voeg module by …" te kies

Voeg ook die IP's by:

- HLS_Video_Track

- Videorame Buffer Skryf

- Video raam buffer gelees

- Video tydsberekening kontroleerder

- AXI4-stroom na video-uitgang

- 3 van "Sny"

- Konstante

- 2 van AXI Timer

Stap 27: IP -konfigurasie -instellings

Soos op die foto's getoon

Stap 28: Voeg PS IP -blok by en konfigureer dit

Voeg die ZYNQ7 -verwerkingstelsel by die blokdiagram

wysig die opset:

-

PS-PL-opset

-

HP

- Aktiveer S HP 0

- Aktiveer S HP 1

-

-

Opstelling van die klok

-

PL Stofhorlosies

- FCLK_0 by 100MHz

- FCLK_1 by 25MHz (OutputClock)

- FLCK_2 by 35MHz (<= 50MHz) (CameraClock)

-

Stap 29: Deel 1. Bou 'n PWM -module vir Servomotors

Bring axi_timer_0 pwm0 na die nuwe uitvoerpoort pwm_Xaxis

Bring axi_timer_1 pwm0 na die nuwe uitvoerpoort pwm_Zaxis

Stap 30: Sy -aansluitings vir video -invoer (aclk gemerk)

Koppel die IP -blokke van die video -invoerkant korrek

(* hierdie verbindings moet geskep word deur die regte opsies te kies tydens die outomatisering van die verbinding) "aclk" uit die axi_stream_capture gaan na:

- ap_clk op video raam buffer skryf

- ap_clk op HLS -videostroomverwerkingsblok

- *reken op AXI smartconnect IP vanaf die videorame -buffer Skryf na die S_AXI_HP0

- *aclk wat ooreenstem met die kanale van die AXI Interconnect IP vir die S_AXI kanale van die HLS video verwerkingsblok en die video raam buffer skryf S_AXI_HP0_ACLK op die PS blok

Die videostroomsein word eenvoudig in serie verbind vanaf die opneemblok na die Zynq -geheue -koppelvlak.

- Video gaan van opnameblok na HLS -verwerkingsblok.

- Die verwerkte video van die HLS -blok gaan na die raambuffer -skryfblok.

- *Die raambuffer -skryfblok maak verbinding met die HP0 -koppelvlak op die Zynq PS -blok.

- Die m_axis_tuser -sein vanaf die uitset van die opneemblok word handmatig aan beide die video_in_TUSER -invoersein op die HLS -verwerkingsblok en die ap_start -sein op dieselfde blok gekoppel.

Die TUSER (tuser) sein word deur die AXI videostroom protokol gebruik om die begin van 'n raam van die video aan te dui. AP_Start sê die HLS blok moet begin verwerk. Ons gebruik dus tuser om die HLS blok te aktiveer om elke raam te verwerk kom in. As u 'n enkele sein van 'n bus aansluit en dit op hierdie manier verdeel, is dit ook nodig om die normale eindpunt van die res van die bus aan te sluit. Vivado veronderstel dat as u die sein handmatig verbind dat u wil ontkoppel waaraan dit normaalweg sou aansluit.

Konfigurasie -instellings van IP -blokke:

Video raam buffer skryf:

Videoformate: RGB8

1 monster per klok Max kolomme: 1280 (> = 640) Max rye: 960 (> = 480) Max data breedte: 8

Stap 31: Verbindings met OV7670

Op die ov7670_axi_stream_capture -blok

- Maak alle insette ekstern (klik met die rechtermuisknop op 'n speld en kies in die spyskaart, of klik met die linkermuisknop-> ctrl+T)

- Laat die name soos hulle is

Op die ov7670_controller -blok

- Maak al die blokuitsette ekstern

- Hernoem die config_finished -poort na led0

- koppel clk aan die CameraClock (<= 50MHz) (FCLK_2)

Op die debounce -blok

- verbind die knoppie 1 -invoer met 'n eksterne invoerpoort genaamd btn0

- verbind out1 met die re -stuurlyn op die ov7670_controller IP -blok

- koppel die knoppie 2 -invoer aan 'n eksterne invoerpoort genaamd btn3

- verbind die out2n met die ext_reset_in -invoer op die verwerkerstelsel -herstel -IP vir die video -opnameklokdomein. (*Dit moet moontlik gedoen word nadat die IP gegenereer is)

- koppel clk aan die CameraClock (<= 50MHz) (FCLK_2)

Stap 32: Verbindings aan die buitekant van die video

Aansluitings vir blokke Video Timing Controller (VTC), AXI4-Stream to Video Out en snye

- Gebruik 'n 25MHz -klok (FCLK_1) vir vid_io_out_clk en VTC clk

- Gebruik 'n 100MHz-klok (FCLK_0) vir ACLK op AXI4-Stream to Video Out

- vtiming_out na vtiming_in

- Video Frame Buffer Lees m_axis_video gaan na AXI4-Stream na Video Out video_in

- vtg_ce gaan na gen_clken

- Bind VTC clken, aclken, vid_io_out_ce aan Constant dout [0: 0]

- Bring vid_hsync en vid_vsync na onderskeidelik eksterne uitvoerpoort vga_hs en vga_vs. (nie op die foto nie)

Snye:

-

Die snye moet opgestel word soos in die aangehegte foto's

- hernoem die blokke na slice_red, slice_green en slice_blue

- opstel sny reekse soos getoon in die beelde volgens die naam van die blok

- koppel elke sny -uitset aan 'n eksterne poort -uitvoer soos in die prentjie getoon.

- vid_data [23: 0] sluit aan by die insette vir elke sny (Din [23: 0])

Stap 33: Begin blok- en verbindingsautomatisering

Begin Block Automation om die dinge van die ZYNQ7 PS -blok aan te sluit. Soos op die foto getoon.

Begin verbindingsoutomatisering om alle onderlinge verbindings -IP te skep. Gee aandag aan alle opsies in elke prent.

Koppel out2n op die debounce -blok aan die video -opnameklokdomein Verwerkerstelsel herstel ext_reset_in -invoer.

Stap 34: Genereer HDL Wrapper

Genereer die HDL Wrapper vir u blokontwerp.

Stel dit as die boonste module.

Stap 35: Genereer Bitstream, voer hardeware uit na SDK, begin SDK vanaf Vivado

Maak seker dat u bitstream by uitvoer insluit.

Die opwekking van bitstroom kan baie lank neem.

Begin dan SDK

Stap 36: SDK (geen FreeRTOS)

Hierdie weergawe doen alles sonder om FreeRTOS te gebruik, en kondenseer die kode mooi.

Skep 'n selfstandige BSP gebaseer op die hardeware -ontwerp. Die standaard opsies moet goed wees. Maak seker dat BSP -bronne gegenereer is.

Skep 'n app soos in die prentjie getoon. (leë aansoek)

Verwyder die outomaties gegenereerde hoof en voer die aangehegte lêers in.

Stap 37: FreeRTOS -implementering

Hierdie weergawe gebruik wel FreeRTOS. Create a FreeRTOS901 BSP based on the hardware design. Die standaard opsies moet goed wees. Maak seker dat BSP -bronne gegenereer is.

Skep 'n app soos in die prentjie getoon. (leë aansoek)

Vee die outomatiese hoofstroom uit en voer die aangehegte lêers in.

Stap 38: Gebruiksinstruksies

Hierdie projek is 'n bietjie moeilik om aan die gang te kom. Volg die stappe in volgorde.

Maak seker dat u ZYBO niks self laai as dit aangeskakel word nie. Dit beteken dat die Done -LED nie moet brand nie. Een manier om dit te doen is om die opstartbron -springer op JTAG te stel.

Maak die projek oop (FreeRTOS of nie) wat u vanaf SDK wil programmeer

- Skakel jou ZYBO aan. Die Klaar LED moet nie brand nie.

- Programmeer die FPGA met die bit -lêer. Die klaar LED moet brand. Led0 moet nie brand nie.

- Begin die kode (onthou om verby die beginpunt te gaan as u dit doen).

Op hierdie punt behoort u 'n uitset op u VGA -skerm te kry.

Om weer te begin (as daar foute is of nie): tik vinnig op die PS-SRST-knoppie of skakel die ZYBO uit en weer aan. Gaan voort vanaf stap 2.

Deur die verwerker te stop met die ontfouter, sal die kamera posisie in plaas van beweeg. Die videostroom sal in elk geval voortgaan.

Stap 39: Verwysings en skakels

Xilinx verwysingsgidse en dokumentasie:

- PG044 - AXI -stroom na video -uitgang

- PG278 - Videorame -buffer lees/skryf

Ander skakels:

- Lauri se blog - VDMA -insette

- Lauri se blog - OV7670 na VGA -uitset met BRAM

- Hamsterworks wiki, deur Mike Fields, die oorspronklike bron van die OV7670 -kode

- Gegewensblad met basiese tydsberekening spesifikasies

Aanbeveel:

Ten volle outomatiese fotografie pan: 14 stappe (met foto's)

Ten volle outomatiese fotografie -panering: inleiding Hi alles, dit is my outomatiese kamera -panering -tuig! Is u 'n ywerige fotograaf, wat 'n begeerte het na een van die baie oulike outomatiese panele, maar dit is regtig duur, soos £ 350+ duur vir twee as panning? Wel, stop hier

WIDI - Draadloos HDMI met behulp van Zybo (Zynq Development Board): 9 stappe (met foto's)

WIDI - Draadlose HDMI met behulp van Zybo (Zynq Development Board): het u al ooit gewens dat u u TV as 'n eksterne monitor aan 'n rekenaar of skootrekenaar kon koppel, maar wou u nie al die lastige toue in die pad hê nie? As dit die geval is, is hierdie tutoriaal net vir u! Alhoewel daar 'n paar produkte is wat hierdie doel bereik, is 'n

Pan- en kantelmeganisme vir DSLR -tydsverloop: 7 stappe (met foto's)

Pan- en kantelmeganisme vir DSLR -tydsverloop: ek het 'n paar stapmotors laat lê en wou dit regtig gebruik om iets cool te maak. Ek het besluit dat ek 'n Pan and Tilt -stelsel vir my DSLR -kamera sal maak, sodat ek 'n koel tydsverloop kan skep. Items wat u benodig: 2x stapmotors -htt

Pan-Tilt Multi Servo Control: 11 stappe (met foto's)

Pan-Tilt Multi Servo Control: In hierdie tutoriaal gaan ons ondersoek hoe u verskeie servo's kan beheer met behulp van Python op 'n Raspberry Pi. Ons doel is 'n PAN/TILT -meganisme om 'n kamera ('n PiCam) te posisioneer. Hier kan u sien hoe ons finale projek sal werk: Control Servo Control lustoets:

Laserharp -sintetiseerder op Zybo -bord: 10 stappe (met foto's)

Laserharp -sintetiseerder op Zybo Board: In hierdie handleiding sal ons 'n volledig funksionele laserharp skep met behulp van IR -sensors met 'n seriële koppelvlak waarmee die gebruiker die stem en toon van die instrument kan verander. Hierdie harp sal die 21ste -eeuse remake van die eeue oue instrument wees. Die