INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:27.

- Laas verander 2025-01-23 12:53.

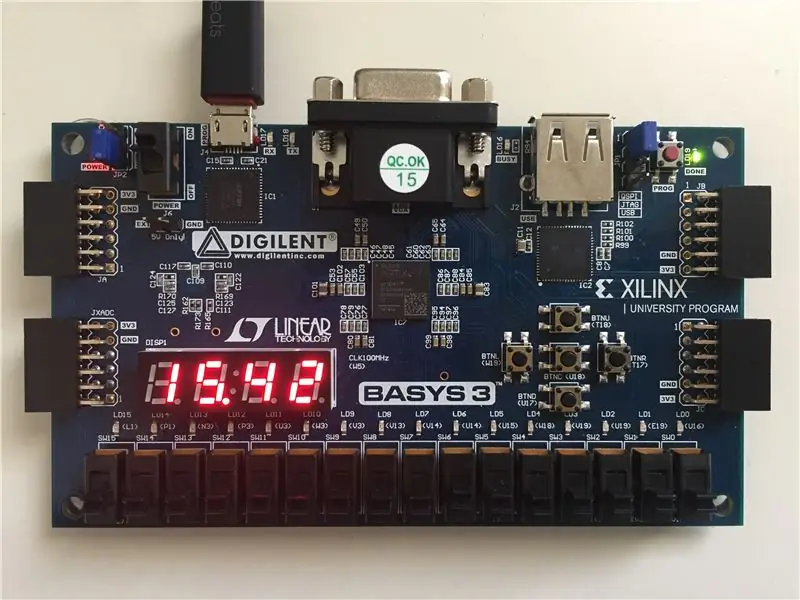

Dit is 'n handleiding oor hoe u 'n stophorlosie kan maak met behulp van VHDL en 'n FPGA-printplaat, soos 'n Basys3 Atrix-7-bord. Die stophorlosie kan van 00,00 sekondes tot 99,99 sekondes tel. Dit gebruik twee knoppies, een vir die begin/stop -knoppie en die ander vir die reset -knoppie. Die getalle word op die bord se sewesegment vertoon met behulp van die anodes en katodes. Daar is drie verskillende lêers nodig om hierdie stophorlosie te laat werk.

Stap 1: Hardeware/sagteware

- Basys3 Atrix-7 FPGA Board

- Vivado Design Suite van Xilinx

- USB 2.0 A Man na Micro-B Male

Stap 2: Blokdiagram

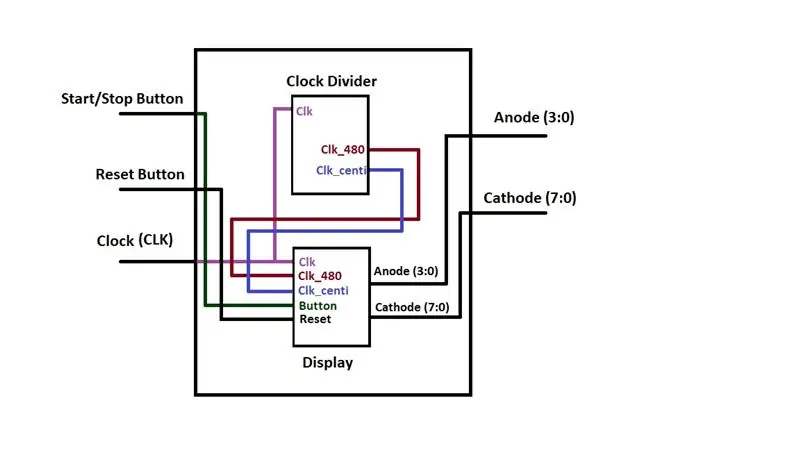

Die algehele stophorlosie het drie insette en twee uitgange. Die drie insette is die begin/stop, reset en klok. Die begin/stop en die reset is knoppies en die horlosie is die bord se 100MHz -klok. Die twee uitsette is die anodes en katodes vir die sewesegment.

Die eerste module (klokverdeler) het een ingang en twee uitsette. Die ingang is die bord se 100MHz -klok en die uitsette is twee afsonderlike horlosies, een wat op 480Hz werk en 'n ander met 0,5MHz.

Die tweede module (skerm) het vyf insette en twee uitsette. Die insette is die 100MHz -horlosie van die bord, die twee horlosies van die klokverdelermodule en die begin/stop- en resetknoppies. Die uitsette is die anodes en katodes.

Die laaste module (gemodelleer deur die hele blokdiagram) het drie insette en twee uitsette. Dit is die lêer wat alles bymekaar bring. Die insette is die 100 MHz van die bord en die knoppies begin/stop en herstel. Die uitsette is die anodes en katodes wat die sewesegment vertoon. Al die insette en uitsette is fisies op die bord vir die finale module.

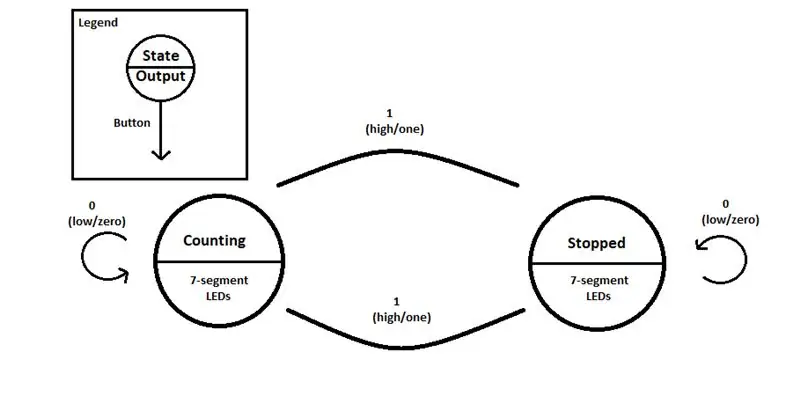

Stap 3: Gee diagram

Die foto hierbo toon die toestand diagram vir hoe die stophorlosie werk. As u op die reset -knoppie druk, het dit geen invloed op die toestand van die stophorlosie nie. Die volgende toestand word bepaal deur die start/stop -knoppie. Die begin/stop is "HOOG" as dit ingedruk word, maar nie as dit ingedruk word nie, en "LAAG" as die knoppie teruggekeer word of ingedruk word nadat dit 'HOOG' was.

As die stophorlosie tel en die begin/stop -knoppie "HOOG" gaan, dan stop dit met tel. As die stophorlosie gestop word en die start/stop -knoppie "HOOG" gaan, begin dit weer tel. As die begin/stop -knoppie vir beide state 'LAAG' is, bly dit in die toestand waarin dit tans is.

Stap 4: Klokverdelermodule

Die klokverdelermodule het een ingang, die bord se 100MHz -horlosie en twee uitsette, die 480Hz- en die 0.5MHz -horlosies. Die 480Hz-klok word gebruik om al die LED's op die sewesegment op dieselfde tyd "aan" te hou deur vinnig deur die vier te skakel. Die 0,5MHz-klok word gebruik om die stophorlosie eintlik met sentisekondes te tel.

Stap 5: Vertoonmodule

Hierdie vertoonmodule het vyf insette, die kaart se 100MHz -horlosie, die twee horlosies van die klokmodule, en die begin/stop- en resetknoppies, en twee uitsette, die anodes en katodes. Hierdie module het ook die 'logika' vir hoe die stophorlosie tel en die eindtoestandmasjien bevat.

Stap 6: Bindmodule

Hierdie laaste module is die een wat die ander twee modules bymekaar bring. Dit het drie insette, die kaart se 100MHz -klok en die begin/stop- en resetknoppies, en twee uitgange, die anodes en katodes. Die 100MHz -klok gaan na die klokverdelermodule en die vertoningsmodule, en die knoppies begin/stop en herstel gaan na die vertoonmodule. Die uitsette van die klokverdelermodule (480Hz en 0.5MHz) gaan na die twee klokinsette van die vertoningsmodule. Die uitsette van die vertoonmodule (anodes en katodes) gaan na die uitsette van die finale module.

Stap 7: Beperkings

Die twee insette kan enige knoppies op die Basys3 Atrix-7 FPGA-bord wees, en die uitsette sal die vier anodes en die agt katodes wees (omdat u ook 'n desimale punt tussen sekondes en millisekondes wil hê) vir die sewesegment.

Stap 8: Klaar

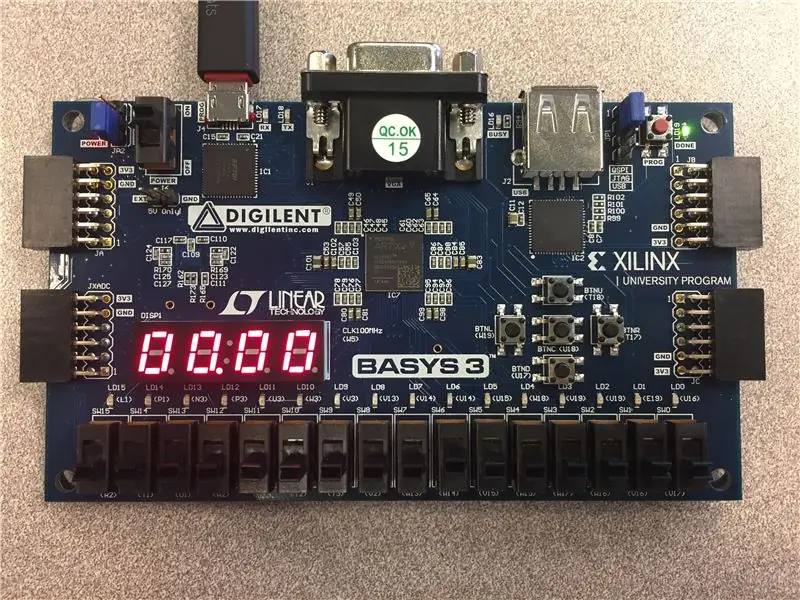

Laai die program op u Basys3 Atrix-7 FPGA-bord op en druk op u start/stop-knoppie om die stophorlosie aan die gang te kry!

Aanbeveel:

Neem wonderlike foto's met 'n iPhone: 9 stappe (met foto's)

Neem wonderlike foto's met 'n iPhone: die meeste van ons dra deesdae 'n slimfoon oral, daarom is dit belangrik om te weet hoe u u slimfoonkamera kan gebruik om fantastiese foto's te neem! Ek het net 'n paar jaar 'n slimfoon gehad, en ek hou daarvan om 'n ordentlike kamera te hê om dinge te dokumenteer wat ek

Raspberry Pi -boks met koelventilator met CPU -temperatuuraanwyser: 10 stappe (met foto's)

Raspberry Pi Box of Cooling FAN Met CPU Temperature Indicator: Ek het framboos pi (Hierna as RPI) CPU temperatuur aanwyser stroombaan in die vorige projek bekendgestel. Die kring wys eenvoudig RPI 4 verskillende CPU temperatuur vlakke soos volg.- Groen LED aangeskakel wanneer CPU temperatuur is binne 30 ~

Howto: Raspberry PI 4 Headless (VNC) installeer met Rpi-imager en foto's: 7 stappe (met foto's)

Howto: Raspberry PI 4 Headless (VNC) installeer met Rpi-imager en foto's: ek is van plan om hierdie Rapsberry PI te gebruik in 'n klomp prettige projekte in my blog. Kyk gerus daarna. Ek wou weer my Raspberry PI gebruik, maar ek het nie 'n sleutelbord of muis op my nuwe plek gehad nie. Dit was 'n rukkie sedert ek 'n Framboos opgestel het

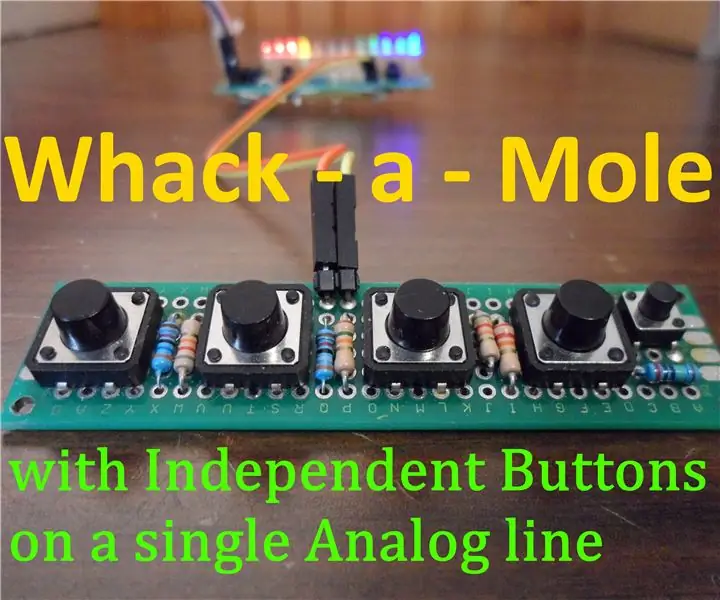

Spel met 4 knoppies met een analoog invoer: 6 stappe (met foto's)

Spel met 4 knoppies met een analoog invoer: hierdie instruksies fokus op die gebruik van een analoog invoerlyn vir verskeie knoppies wat onafhanklik van mekaar opgespoor kan word. Al die speletjies (8 in t

Hoe om 'n rekenaar met maklike stappe en foto's uitmekaar te haal: 13 stappe (met foto's)

Hoe om 'n rekenaar uitmekaar te haal met eenvoudige stappe en foto's: dit is 'n instruksie oor hoe om 'n rekenaar uitmekaar te haal. Die meeste basiese komponente is modulêr en kan maklik verwyder word. Dit is egter belangrik dat u daaroor georganiseerd is. Dit sal u verhinder om onderdele te verloor, en ook om die montering weer