INHOUDSOPGAWE:

- Outeur John Day day@howwhatproduce.com.

- Public 2024-01-30 07:26.

- Laas verander 2025-01-23 12:53.

Ek weet wat jy dink: "Huh? Daar is baie instruksies oor hoe om mikrobeheerders te gebruik om seinfrekwensie te meet. Gaap." Maar wag, daar is 'n nuwigheid hierin: ek beskryf 'n metode om frekwensies te meet wat veel hoër is as wat 'n mikrobeheerder (MCU) kan dra en die seiklus van die sein - terselfdertyd!

Die frekwensiebereik van die toestel strek van ~ 43 Hz tot ~ 450 kHz, terwyl die dienssiklus wissel van 1% tot 99%.

Laat ek die gedeelte "kan dra" verduidelik: 'n MCU meet die tydperk van 'n vierkantgolfsein, T, deur die tyd tussen twee daaropvolgende oorgangsgebeure op te spoor. Laag-tot-hoogspanning spring byvoorbeeld op een van sy I/O-penne. Dit word gedoen deur die aantal pulse van sy eie interne klok te tel. Naïef moet die boonste grens vir gemete frekwensies die Nyqvist-Shannon-steekproefstelling volg; dit wil sê, dit sal ongeveer gelyk wees aan die helfte van die MCU se klokfrekwensie. In werklikheid is die limiet baie, baie laer, omdat die MCU kode moet uitvoer om onderbrekings te hanteer, veranderlikes te stoor, rekenkundige bewerkings te doen, resultate te vertoon, ens. In my eksperimente met 'n 48 MHz MCU was die minimale aantal kloksiklusse tussen meetbare oorgange ongeveer 106. Daarom sou die boonste grens van die meetbare frekwensiebereik in hierdie geval 48 000 /212 /2 = 226,4 kHz wees.

Terwyl die MCU die tydperk van die sein meet, kan dit ook die polswydte P bepaal: die tyd waarin die seinspanning hoog bly. Met ander woorde, tyd tussen laag-na-hoog en hoog-na-laag oorgange. Die seinsiklus van die sein word dan gedefinieer as die volgende persentasie:

Plig = 100% * P / T

Net soos in die geval van frekwensie, is daar 'n praktiese beperking op die pulswydte. Deur die voorbeeld hierbo te gebruik, sou 106 kloksiklusse die polswydte tot nie minder nie as 2,21 mikrosekondes beperk. Of nie minder nie as 50% by 226,4 kHz.

Een van die maniere om die boonste frekwensiegrens van vierkantgolfseine te verhoog, is die toepassing van digitale verdelers wat flip-flops gebruik. Deur die invoerfrekwensie deur n te deel, sou die meetbare boonste reeks n keer verleng word. Dit is wonderlike nuus, digitale verdelers het een fundamentele gebrek: verdeelde sein verloor die polswydte (en dienssiklus) inligting! As gevolg van die manier waarop die verdelers werk, het hul uitset altyd 'n 50% -siklus. Jammer…

Op die volgende bladsye sal ek egter wys hoe om die frekwensie digitaal te verdeel en die oorspronklike polswydte te behou, sodat ek seine kan meet ver buite die grense wat deur direkte tellings opgelê word.

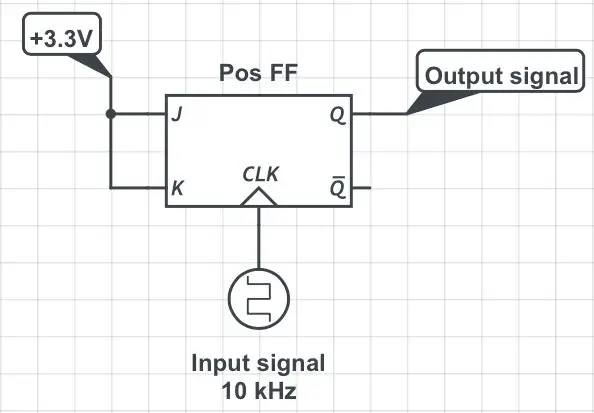

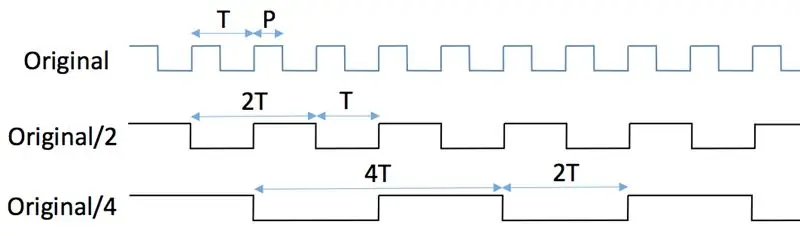

Stap 1: Afdeling Digitale Frekwensie

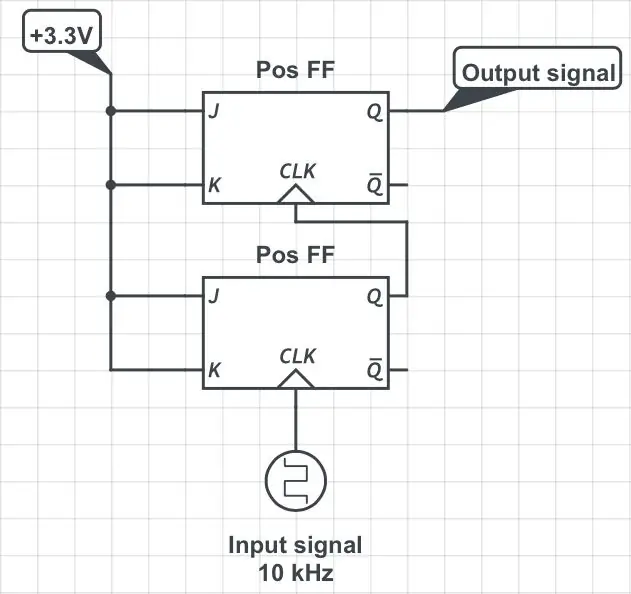

Tradisionele digitale frekwensieverdelers gebruik flip-flops; hierdie handleiding verduidelik die beginsels van hoe om verdelers te bou met behulp van standaard JK-flip-flops. Dit los die probleem van insetfrekwensies te hoog vir die MCU op, maar het 'n groot nadeel: verdeelde sein het 'n 50% -siklus, ongeag die insetsein se plig! Kyk na die eerste twee syfers om te sien waarom dit die geval is. Die oorspronklike sein met tydperk T en polswydte P word ingevoer in die klokpen van 'n JK-flip-flop terwyl sy J- en K-penne te alle tye hoog gehou word (eerste figuur). 3.3V logika word deurgaans aanvaar. Gestel die flip-flop word veroorsaak deur die positiewe (d.w.s. stygende) rand van die klok. Onder hierdie omstandighede vind veranderinge in die toestand van die uitvoerpen (individuele "flips" en "flops") plaas elke keer as die klokpen van laag na hoog gaan. Die hoë na lae oorgang van die klok (dit wil sê die negatiewe rand) word heeltemal geïgnoreer. Sien die tweede figuur. Die uitvoerpen, Q, gee 'n sein uit waarvan die tydperk twee keer so lank is as die oorspronklike periode, dit wil sê dat die frekwensie daarvan gehalveer word. Die uitgang se polswydte is altyd gelyk aan T. Gevolglik gaan die oorspronklike polswydte, P, verlore.

As u nog 'n JK-flip-flop byvoeg in 'n opset wat in die derde figuur getoon word, verdeel die oorspronklike frekwensie met 4. As u meer flip-flops op dieselfde opeenvolgende manier byvoeg, word die frekwensie gedeel deur die volgende krag van 2: 8, 16, 32, ens.

Probleem: hoe om die frekwensie van 'n vierkantgolf te verdeel terwyl die polswydte behoue bly?

Die idee is om 'n JK-flip-flop met 'n negatiewe rand by die mengsel te voeg. Kom ons noem dit "Neg FF"; sien vierde figuur. Hier beteken "behoorlik" dat die J- en K-penne van die nuwe flip-flop vasgemaak is aan die Q- en Qbar-uitvoerpenne, onderskeidelik, van die divider-by-4 ("Pos FF") wat in die vorige figuur geïllustreer is. (Hier is "balk" die horisontale balk oor die Q -simbool wat logiese ontkenning aandui.) Kyk na die funksietabel van die "Neg FF" in die vyfde figuur: Neg se uitsetpenne, Q en Qbar, weerspieël die toestand van die invoerpenne, onderskeidelik J en K. Dit beteken dat hulle die toestand van die Pos se Q en Qbar weerspieël. Maar die Neg se flip-flop-aksie moet wag op die negatiewe rand van die oorspronklike sein, wat op die tyd P na die positiewe rand kom. Aha!

Die gevolglike golfvorme word in die sesde figuur geïllustreer. "Pos Q" uitsette seine op 1/4de frekwensie, "Pos Qbar" is dit omgekeerd, "Neg Q" volg op "Pos Q" verskuif deur polswydte P, en "Neg Qbar" is sy inverse. U kan verifieer dat die logiese EN van "Pos Qbar" en "Neg Q" 'n polsstrein oplewer wat gekenmerk word deur die oorspronklike polswydte P en 1/4 van die frekwensie. Bingo!

Ek het eers presies hierdie uitsetsignaal gebruik om die MCU te voed. Dit blyk egter problematies te wees vir baie kort polswydtes as gevolg van die MCU se 106 siklusbeperkings wat in die inleiding genoem word. Ek het hierdie klein probleem opgelos deur 'n ander uitset te kies: "Pos Qbar" EN "Neg Qbar". Een blik op die golfvorms moet u oortuig dat die pulswydte van hierdie spesifieke golfvorm, P ', wissel tussen T en 2T in plaas van die (0, T) reeks vir P. Die P kan maklik van P' herwin word deur:

P = 2T - P '

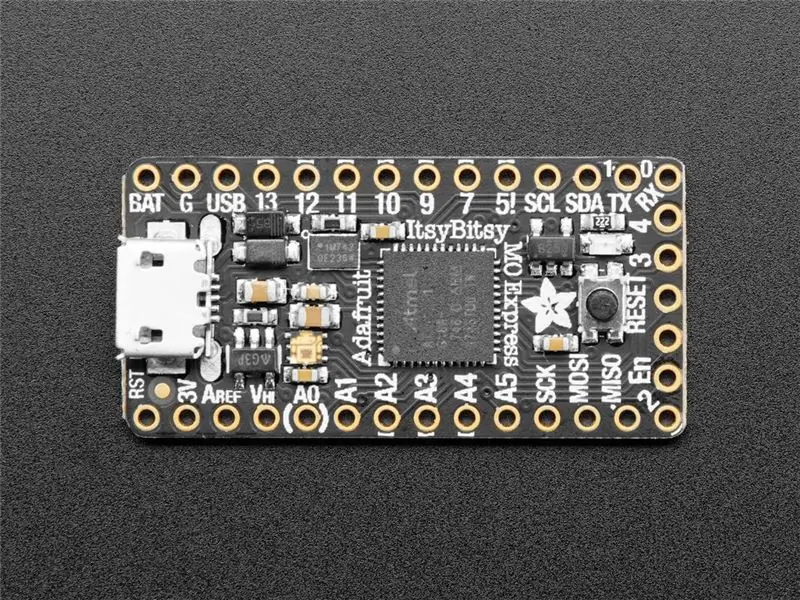

Stap 2: Aanbevole hardeware

Ek hou regtig van die relatiewe nuweling by elektroniese stokperdjies: Atmel SAM D21 MCU's gebaseer op die 32-bis ARM Cortex M0+ -verwerker wat werk met 'n 48 MHz kloksnelheid, baie hoër as die ouer Atmels. Vir hierdie projek het ek gekoop:

- ItsyBitsy M0 Express MCU -bord van Adafruit

- Ek het toevallig 'n herlaaibare LiPo -battery van Adafruit gehad

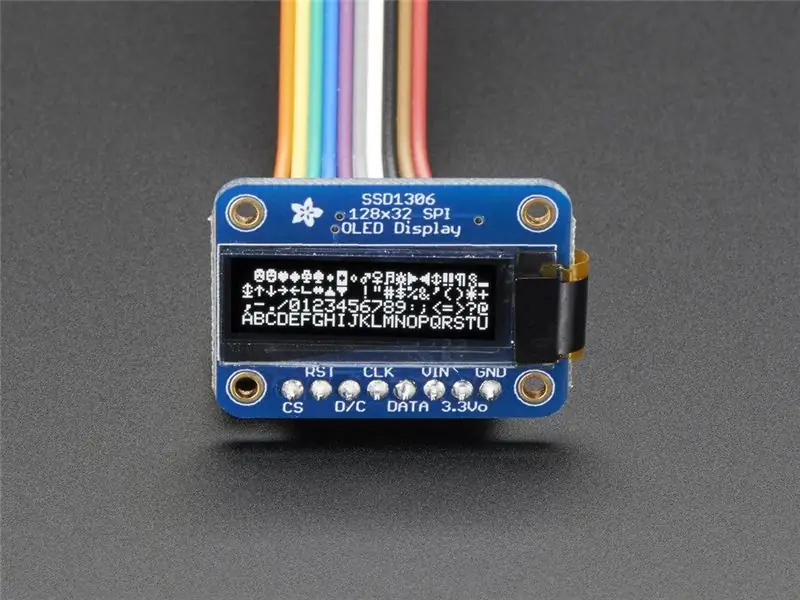

- Monochroom 128x32 SPI OLED -skerm (jy raai dit: Adafruit)

- Dubbele positiewe rand-geaktiveerde JK-flip-flop SN74HC109 van Texas Instruments

- Dubbele negatiewe rand-geaktiveerde JK-flip-flop SN74HC112 van Texas Instruments

- Viervoudig EN hek CD74AC08E van Texas Instruments

- Viervoudige OF hek CD74AC32E van Texas Instruments

Stap 3: Die stroombaan

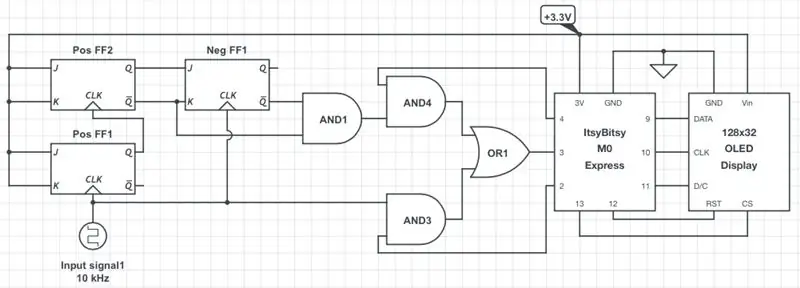

Die eerste figuur toon 'n vereenvoudigde skematiese voorstelling van die frekwensie/ploegmeter. Die 3.3 V CMOS -logika word deurgaans aanvaar. Gevolglik moet die amplitude van die invoervierkantgolf tussen die ooreenstemmende V weesIH vlak (dws 2 V) en 3,3 V. Indien nie, moet u dit dienooreenkomstig op of af skaal. In die meeste gevalle is 'n eenvoudige spanningsverdeler voldoende. As u u weergawe van die meter op 'n ander logiese vlak wil ontwerp, moet u 'n ander mikrobeheerder (MCU), 'n battery en 'n skerm gebruik wat op die gewenste vlak werk. Die logiese hekke en flip-flops wat in hierdie projek gebruik word, werk met logiese vlakke tussen 2 V en 6 V en behoort in die meeste gevalle reg te wees.

Soos getoon, gebruik die ItsyBitsy MCU penne 9-13 om met die skerm te kommunikeer deur middel van die sagteware SPI-protokol. Die 3V -pen lewer krag aan die hele stroombaan. Digitale invoerpen 3 aanvaar die geanaliseerde sein, terwyl penne 2 en 4 die seinbron beheer: óf direkte sein wat deur hek AND3 kom (lae insetfrekwensies), óf sein gedeel deur 4 deur hek AND4 (hoë insetfrekwensies) soos beskryf in stap 2 Die kode, wat in die volgende stap bespreek word, bespeur outomaties die inkomende frekwensiebereik en skakel die seinbron behoorlik oor.

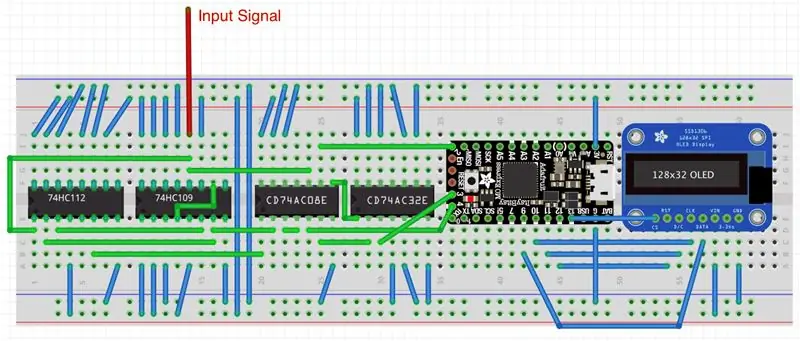

Die skema toon nie die ware kompleksiteit van digitale skyfverbindings nie. Die tweede prent wys hoe die projek op 'n broodbord sou lyk. Insetsein kom deur 'n rooi draad na die 2CLK-pen van die dubbele flip-flop. LET WEL: Normaalweg moet al die J- en K -penne van hierdie flip -flop hoog gehou word, maar veral SN74HC109 bevat die Kbar -pen - 'n omgekeerde K -pen - in plaas daarvan. Daarom moet hierdie pen gegrond wees! Die eerste negatiewe rand-flip-flop in SN74HC112 het sy 1K- en 1J-pen gekoppel aan die 1Q- en 1Qbar-penne van SN74HC109. Die tweede flip-flop in SN74HC112 is ongebruik en die invoerpenne (2K, 2J, 2CLRbar) is gegrond. Alle ander ekstra penne PREbar (vooraf ingestel) en CLRbar (duidelik) in alle flip-flops moet aan logiese high gekoppel word. Ongebruikte horlosie en uitsetpenne word sonder verbinding gelaat. Net so word ongebruikte invoerpenne in alle hekke geaard, terwyl ongebruikte uitsetpenne nie verbind is nie. Soos ek bespreek het in my "Invisible Killer of the Phone Ring" Instructable, elimineer ongebruikte invoerpenne van logiese skyfies deur willekeurige ossillasies en bespaar batterykrag.

Stap 4: Die kode en die meting van lae frekwensies

Natuurlik gebeur al die aksies in die onderstaande kode. As die ingang wat op pen 3 inkom, van digitaal laag na hoog skakel, begin die MCU pulse van sy interne 48 MHz -klok tel. Dit merk op die oomblik van hoë na lae oorgang en gaan voort met die telling tot die volgende laag na hoë skakelaar, wanneer dit die hele proses weer begin. Die eerste telling verteenwoordig polswydte, terwyl die hele telling die tydperk van die sein voorstel. En dit is die hele geheim.

Die SVE neem kennis van hierdie oorgange deur hardeware -onderbrekings. Die SAMD21 het verskeie horlosies; my kode gebruik TC3 one. Aanvanklik het ek begin met die lees van die datablad van die M0 vir baie moeite om die interrupt -hanteerder te kodeer, maar ek het gou 'n baie verwante kode ontdek in die Arduino Forum -poste deur gebruikers electro_95, MartinL en Rucus wie se bydrae behoorlik erken. Ek het die gekombineerde kode daarvan in my opgeneem en verander; spaar my baie tyd!

Soos ek vroeër genoem het, is die seinresolusie beperk deur ~ 106 CPU -siklusse om kode tussen onderbrekings uit te voer. Digitale verdeling met die behoud van die pulswydte sorg vir hoë frekwensies. Lae frekwensies, aan die ander kant, bied 'n ander uitdaging: aangesien die TC3 -klokteller 16 bit lank is, loop dit oor nadat hy die 65, 536 tellingslimiet oorskry het. U kan hierdie situasie hanteer deur 'n oorlooponderbreking by te voeg, maar 'n ander oplossing kies: TC3 kan 'n vooraf geskaalde (met sagteware-verdeelde) CPU-klok gebruik in plaas van die hardeware van 48 MHz. As die tydperk van die sein dus die oorloopgrens bereik, kan die kode TC3 opdrag gee om 24 MHz tellings vir die volgende periode te gebruik, en voila, die teller val onder 32, 768 tellings. Vir nog laer frekwensies kan die TC3 opdrag gegee word om 12 MHz pulse, ens. Te tel. Die toepaslike prescaler word outomaties bepaal op grond van die frekwensie van die sein, met histerese, om die TC3 -teller binne die oorloopgrens te hou. As gevolg hiervan is die onderste punt van die toestel se reeks ongeveer 43 Hz.

U is welkom om die kode te vurk en dit in u projek te gebruik, maar noem die bron daarvan as u resultate publiseer.

Skakel na die kode.

Aanbeveel:

Hoe om die kragverbruik van draadlose kommunikasiemodules korrek te meet in die era van lae kragverbruik ?: 6 stappe

Hoe om die kragverbruik van draadlose kommunikasiemodules korrek te meet in die era van lae kragverbruik?: Lae kragverbruik is 'n uiters belangrike konsep in die Internet of Things. Die meeste IoT -nodusse moet deur batterye aangedryf word. Slegs deur die kragverbruik van die draadlose module korrek te meet, kan ons akkuraat skat hoeveel battery ek

Konfigurasie van die AVR -mikrobeheerder. Skep en laai die LED -knipperprogram in die flitsgeheue van die mikrokontroleerder op: 5 stappe

Konfigurasie van die AVR -mikrobeheerder. Skep en laai die LED -knipperprogram in die flitsgeheue van die mikrokontroleerder: In hierdie geval sal ons 'n eenvoudige program in C -kode skep en dit in die geheue van die mikrokontroleerder verbrand. Ons sal ons eie program skryf en die hex -lêer saamstel, met behulp van die Atmel Studio as die geïntegreerde ontwikkelingsplatform. Ons sal die sekering van twee instel

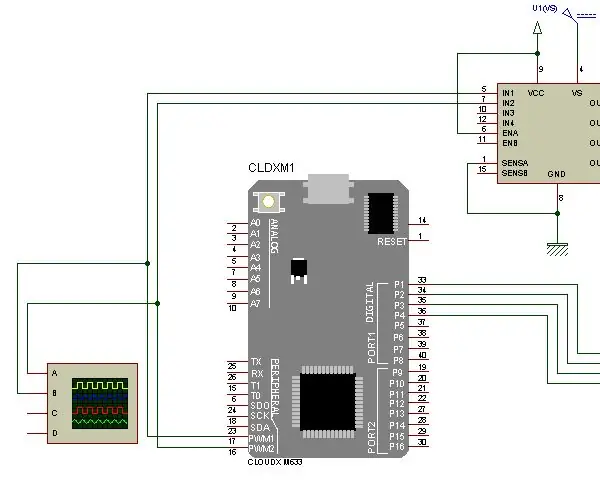

Die beheer van DC -motors met die L298N met behulp van CloudX -mikrobeheerder: 3 stappe

Die beheer van DC-motors met die L298N met behulp van CloudX-mikrobeheerder: In hierdie projek sal ons verduidelik hoe ons ons L298N H-brug kan gebruik om die spoed van die DC-motor te verhoog en te verlaag. Die L298N H-brugmodule kan gebruik word met motors met 'n spanning tussen 5 en 35V DC. Daar is ook 'n ingeboude 5V-reguleerder, so as u

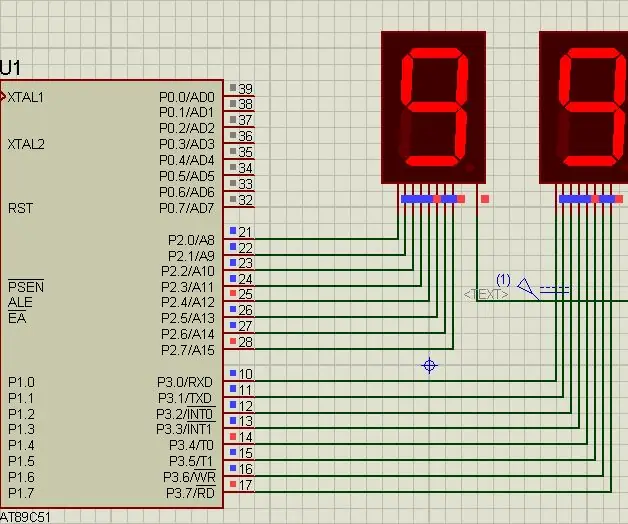

Hoe om van 0 tot 99 te tel met behulp van 8051 mikrobeheerder met 7 segmentweergawe: 5 stappe (met foto's)

Hoe om van 0 tot 99 te tel Met behulp van 8051 mikrobeheerder met 7 -segmentweergawe: Hallo almal, in hierdie tutoriaal gaan ons u vertel hoe om van 0 tot 99 te tel met twee 7 -segment -skerms

Instruksies vir die voltooiing van die opmaak van die baanskyfontwerp vir die opheffing/verlaging van die middelste voetsteun op motorwielstoele: 9 stappe (met foto's)

Instruksies vir die voltooiing van die opmaak van die baanskyfontwerp vir die opheffing/verlaging van die middelste voetsteun op motorwielstoele: die middelste voetsteunhysers moet goed onder die sitplek geberg word en laer om te ontplooi. 'N Meganisme vir die onafhanklike werking van die opberging en ontplooiing van voetsteun is nie ingesluit by rolstoele op die mark nie, en PWC -gebruikers het die behoefte uitgespreek